AD8250

10MHz

、

20V/µs

の

iCMOS

®

計装アンプ

特長

小型パッケージ:10ピンMSOP ゲイン設定可能:1、2、5、10 ゲインをデジタルまたはピンにより設定 広い電源電圧範囲:±5∼±15V 優れたDC性能 高CMRR:最小98dB、G=10 低ゲイン・ドリフト:最大10ppm/℃ 低オフセット・ドリフト:最大1.7µV/℃、G=10 優れたAC性能 高速セトリング時間:0.001%までで最大615ns 高スルーレート:最小20V/µs 低歪み:1kHzでTHD=−110dB 周波数全域で高CMRR:50kHzまで最小80dB 低ノイズ:最大18nV/ 、G=10 低消費電力:4mAアプリケーション

データ・アクイジション バイオメディカル分析 テストおよび計測概要

AD8250は、GΩ入力インピーダンス、低出力ノイズ、低歪み の特性を持つデジタル・プログラマブル・ゲイン計装アンプ (PGIA)であるため、センサとのインターフェースや高速サン プリング・レートのA/Dコンバータ(ADC)の駆動に最適です。 このデバイスは、10MHzの広帯域幅、−110dBの低THD、 615nsの高速セトリング時間(0.001%)を持っています。オフ セット・ドリフトおよびゲイン・ドリフトは、G=10でそれぞ れ1.7µ V/℃および10ppm/℃です。本製品は広い入力同相電圧 範囲だけではなく、DCから50kHzまで80dB(G=1)という優 れたCMRR(同相ノイズ除去)性能も持っています。高精度の DC性能と高速機能の組み合わせにより、データ・アクイジ ション向けの最適な選択肢になっています。また、このモノリ シック・ソリューションは、設計および製造を簡素化し、内部 抵抗と内部アンプとの高い整合性を維持することにより計測性 能を向上させます。 AD8250のユーザ・インターフェースはパラレル・ポートから 構成されており、ユーザは2種類の方法でゲインを設定するこ とができます(図1の機能ブロック図を参照)。バスを介して送 信される2ビット・ワードは、WR ___ 入力を使ってラッチできます。 また、トランスペアレント・ゲイン・モードを使用して、ゲイ ン・ポートのロジック・レベルの状態でゲインを決めることも できます機能ブロック図

図1 図2. ゲインの周波数特性 表1. 計装/差動アンプの分類High Low High Mil Low Digital Performance Cost Voltage Grade Power Gain AD82201 AD6231 AD628 AD620 AD6271 AD82311

AD8221 AD85531 AD629 AD621 AD8251

AD8222 AD524 AD85551

AD82241 AD526 AD85561

AD624 AD85571 1 レールtoレール出力 AD8250は10ピンMSOPパッケージを採用しており、−40∼ +85℃の温度範囲で仕様が規定されています。本製品は、サイ ズや集積度が重視されるアプリケーションの優れたソリュー ションとなります。 25 –10 –5 0 5 10 15 20 1k 10k 100k 1M 10M 100M ) B d( NI A G FREQUENCY (Hz) G = 10 G = 5 G = 2 G = 1 3 2 0-8 8 2 6 0 A1 A0 DGD WR AD8250 +VS –VS REF OUT +IN LOGIC –IN 1 0 0-8 8 2 6 0 1 10 8 3 7 4 5 6 2 9 Hz

特長 . . . 1 アプリケーション . . . 1 概要 . . . 1 機能ブロック図 . . . 1 改訂履歴 . . . 2 仕様 . . . 3 タイミング図. . . 5 絶対最大定格 . . . 6 最大消費電力. . . 6 ESDに関する注意 . . . 6 ピン配置とピン機能の説明 . . . 7 代表的な性能特性 . . . 8 動作原理 . . . 15 ゲインの選択. . . 15 電源レギュレーションとバイパス. . . 17 入力バイアス電流のリターン・パス. . . 17 入力保護. . . 17 リファレンス・ピン. . . 18 同相入力電圧範囲. . . 18 レイアウト. . . 18 RF干渉 . . . 18 A/Dコンバータの駆動 . . . 19 アプリケーション . . . 20 差動出力. . . 20 マイクロコントローラによるゲインの設定. . . 20 データ・アクイジション. . . 21 外形寸法 . . . 22 オーダー・ガイド. . . 22

目次

改訂履歴

仕様

特に指定のない限り、+VS=+15V、−VS=−15 V、VREF=0V@TA=25℃、G=1、RL=2kΩ。

表2

Parameter Conditions Min Typ Max Unit

COMMON-MODE REJECTION RATIO (CMRR)

CMRR to 60 Hz with 1 kΩ Source Imbalance +IN = – IN = – 10 V to +10 V

G = 1 80 94 dB G = 2 86 104 dB G = 5 94 106 dB G = 10 98 106 dB CMRR to 50 kHz +IN = – IN = – 10 V to +10 V G = 1 80 dB G = 2 86 dB G = 5 90 dB G = 10 90 dB NOISE

Voltage Noise, 1 kHz, RTI

G = 1 40 nV/ G = 2 27 nV/ G = 5 21 nV/ G = 10 18 nV/ 0.1 Hz to 10 Hz, RTI G = 1 2.5 µV p-p G = 2 2.5 µV p-p G = 5 1.5 µV p-p G = 10 1.0 µV p-p

Current Noise, 1 kHz 5 pA/

Current Noise, 0.1 Hz to 10 Hz 60 pA p-p VOLTAGE OFFSET

Offset RTI VOS G = 1, 2, 5, 10 ±200 + 600/G µV

Over Temperature T = – 40℃to +85℃ ±260 + 900/G µV Average TC T = – 40℃to +85℃ ±1.2 + 5/G µV/℃

Offset Referred to the Input vs. Supply (PSR) VS= ±5 V to ±15 V ±6 + 20/G µV/V

INPUT CURRENT

Input Bias Current 5 30 nA

Over Temperature T = – 40℃to +85℃ 40 nA

Average TC 400 pA/℃

Input Offset Current 5 30 nA

Over Temperature T = – 40℃to +85℃ 30 nA

Average TC 160 pA/℃

DYNAMIC RESPONSE Small Signal – 3 dB Bandwidth

G = 1 10 MHz G = 2 10 MHz G = 5 10 MHz G = 10 3 MHz ΔOUT = 10 V step Hz Hz Hz Hz Hz

Parameter Conditions Min Typ Max Unit Settling Time 0.001% ΔOUT = 10 V step

G = 1 615 ns G = 2 635 ns G = 5 635 ns G = 10 685 ns Slew Rate G = 1 20 V/µs G = 2 25 V/µs G = 5 25 V/µs G = 10 25 V/µs

Total Harmonic Distortion f = 1 kHz, RL= 10 kΩ, G = 1 – 110 dB

GAIN

Gain Range G = 1, 2, 5, 10 1 10 V/V

Gain Error OUT = ±10 V

G = 1 0.03 %

G = 2, 5, 10 0.04 %

Gain Nonlinearity OUT = – 10 V to +10 V

G = 1 RL= 10 kΩ, 2 kΩ, 600 Ω 6 ppm

G = 2 RL= 10 kΩ, 2 kΩ, 600 Ω 8 ppm

G = 5 RL= 10 kΩ, 2 kΩ, 600 Ω 8 ppm

G = 10 RL= 10 kΩ, 2 kΩ, 600 Ω 10 ppm

Gain vs. Temperature All gains 10 ppm/℃

INPUT

Input Impedance

Differential 1 GΩ||pF

Common Mode 1 GΩ||pF

Input Operating Voltage Range VS= ±5 V to ±15 V – VS+ 1.0 +VS– 1.1 V

Over Temperature T = – 40℃to +85℃ – VS+ 1.1 +VS– 1.4 V OUTPUT Output Swing – 13.5 +13.5 V Over Temperature T = – 40℃to +85℃ – 13.5 +13.5 V Short-Circuit Current 37 mA REFERENCE INPUT RIN 20 kΩ

IIN +IN, – IN, REF = 0 1 µA

Voltage Range – VS +VS V

Gain to Output 1 ± 0.0001 V/V

DIGITAL LOGIC

Digital Ground Voltage, DGND Referred to GND – VS+ 4.25 0 +VS– 2.7 V

Digital Input Voltage Low Referred to GND DGND 2.1 V Digital Input Voltage High Referred to GND 2.8 +VS V

Digital Input Current 1 µA

Gain Switching Time1 325 ns

tSU See Figure 3 timing diagram 20 ns

tHD 10 ns

tWR__-LOW 20 ns

Parameter Conditions Min Typ Max Unit POWER SUPPLY

Operating Range ±5 ±15 V

Quiescent Current, +IS 4.1 4.5 mA

Quescent Current, –IS 3.7 4.5 mA

Over Temperature T = – 40℃to +85℃ 4.5 mA TEMPERATURE RANGE Specified Performance – 40 +85 ℃ 1 ゲイン変化の全時間は、出力が変化する時間とセトリングする時間を加算したものです。

タイミング図

図3. ラッチ・ゲイン・モードのタイミング図(「ラッチ・ゲイン・モードのタイミング」を参照) A0, A1 WR tSU tHD tWR-HIGH tWR-LOW 07 5 0-8 8 2 6絶対最大定格

表3

Parameter Rating Supply Voltage ±17 V Power Dissipation See Figure 2 Output Short-Circuit Current Indefinite1

Common-Mode Input Voltage ±VS

Differential Input Voltage ±VS

Digital Logic Inputs ±VS

Storage Temperature Range – 65℃to +125℃

Operating Temperature Range2 – 40

℃to +85℃

Lead Temperature (Soldering 10 sec) 300℃

Junction Temperature 140℃

θJA(4-Layer JEDEC Standard Board) 112℃/W

Package Glass Transition Temperature 140℃

1 負荷は電源中央値を基準とします。 2 規定の性能は−40∼+85℃の温度範囲の場合です。+125℃までの性能については、 「代表的な性能特性」を参照してください。 上記の絶対最大定格を超えるストレスを加えると、デバイスに 恒久的な損傷を与えることがあります。この規定はストレス定 格のみを指定するものであり、この仕様の動作セクションに記 載する規定値以上でのデバイス動作を定めたものではありませ ん。デバイスを長時間絶対最大定格状態に置くと、デバイスの 信頼性に影響を与えることがあります。

最大消費電力

AD8250パッケージでの安全な最大消費電力は、チップのジャ ンクション温度(TJ)の上昇によって制限されます。チップを プラスチック封止すると、局所的にジャンクション温度に到達 します。約140℃のガラス転移温度で、プラスチックの属性が 変わります。この温度規定値を一時的にせよ超えた場合は、 パッケージからチップに加えられる応力が変化し、AD8250の パラメータ性能が永久的に変化することがあります。140℃の ジャンクション温度を長時間超えると、シリコン・デバイス内 に変化が発生し、故障の原因になることがあります。 パッケージとPCボードの自然空冷時の熱特性(θJA)、周辺温度 (TA)、パッケージ内の合計消費電力(PD)によって、チップの ジャンクション温度が決定されます。ジャンクション温度は次 式で計算されます。 TJ=TA+(PD×θJA) パッケージ内の消費電力(PD)は、静止消費電力と、全出力で の負荷駆動により発生するパッケージ内の消費電力との和にな ります。静止電力は、電源ピン間の電圧(VS)に静止電流(IS) を乗算して計算されます。負荷(RL)は電源中央値を基準にす ると、合計駆動電力はVS/2×IOUTになり、この電力がパッケー ジ内と負荷(VOUT×IOUT)とで消費されます。 合計駆動電力と負荷電力の差が、パッケージ内で消費される駆 動電力です。 RLが−VSを基準とする単電源動作の場合、最悪時はVOUT=VS/2 となります。 空気流があると放熱効果が良くなりθJAが小さくなります。また、 メタル・パターン、スルー・ホール、グラウンド・プレーン、 電源プレーンからパッケージ・ピンへ直接接続されるメタルが 増えた場合にも、θJAが小さくなります。 図4は、JEDEC規格4層ボードにおける、パッケージ内での安 全な最大消費電力と周辺温度の関係です。 図4. 周辺温度 対 最大消費電力ESD

に関する注意

ESD(静電放電)の影響を受けやすいデバイス です。電荷を帯びたデバイスや回路ボードは、 検知されないまま放電することがあります。本 製品は当社独自の特許技術であるESD保護回路 を内蔵してはいますが、デバイスで高エネル ギーの静電放電が発生した場合、損傷を生じる 可能性があります。性能劣化や機能低下を防止 するため、ESDに対して適切な予防措置をとる ことが推奨されます。 2.00 1.75 1.50 1.25 1.00 0.75 0.50 0.25 0 –40 –20 0 20 40 60 80 100 120 ) W( N OI T A PI S SI D R E W O P M U MI X A M AMBIENT TEMPERATURE (°C) 4 0 0-8 8 2 6 0 PD= PD=Quiescent Power +( Total Drive Power Load Power)

( )

L OUT L OUT S SR

V

R

V

V

V

I

S 2 − 2 × × + −ピン配置とピン機能の説明

図5. 10ピンMSOP(RM-10)のピン配置 表4. ピン機能の説明 ピン番号 記号 説明 1 –IN 反転入力端子。真の差動入力 2 DGND デジタル・グラウンド 3 –VS 負電源端子 4 A0 ゲイン設定ピン(LSB) 5 A1 ゲイン設定ピン(MSB) 6 WR ___ 書込みイネーブル 7 OUT 出力端子 8 +VS 正電源端子 9 REF リファレンス電圧端子 10 +IN 非反転入力端子。真の差動入力 –IN DGND –VS A0 A1 +IN REF +VS OUT WR AD8250 TOP VIEW (Not to Scale) 1 2 3 4 5 10 9 8 7 6 5 0 0-8 8 2 6 0代表的な性能特性

特に指定のない限り、TA@25℃、+VS=+15V、−VS=−15V、RL=10kΩ。 6 0 0-8 8 2 6 0 1400 1200 800 1000 600 400 200 0 S TI N U F O R E B M U N CMRR (µV/V) –120 –90 –60 –30 0 30 60 90 120 500 400 300 200 100 0 –30 –20 –10 0 10 20 30 S TI N U F O R E B M U NINPUT BIAS (nA)

9 0 0-8 8 2 6 0 図6. 代表的なCMRR分布(G=1) 図9. 代表的な入力オフセット電流分布 300 350 250 200 150 100 50 0 –200 –150 –100 –50 0 50 100 150 200 S TI N U F O R E B M U N

OFFSET VOLTAGE RTI (µV)

7 0 0-8 8 2 6 0 90 0 10 20 30 40 50 60 70 80 1 10 100 1000 10000 100000 0 1 0-8 8 2 6 0 ) z H / V n( E SI O N FREQUENCY (Hz) G = 1 G = 2 G = 5 G = 10 図7. 代表的なオフセット電圧分布(VOSI) 図10. 電圧スペクトル密度の周波数特性 600 500 400 300 200 100 0 –30 –20 –10 0 10 20 30 S TI N U F O R E B M U N

INPUT BIAS (nA)

8 0 0-8 8 2 6 0 01 1 0-8 8 2 6 1s/DIV 2µV/DIV 図8. 代表的な入力バイアス電流分布 図11. 0.1∼10Hz時の入力換算電圧ノイズ(G=1)

02 1 0-8 8 2 6 1s/DIV 1µV/DIV 150 130 110 90 70 50 30 10 1 10 100 1k 10k 100k 1M ) B d( R R S P FREQUENCY (Hz) G = 10 G = 5 G = 2 G = 1 6 1 0-8 8 2 6 0 図12. 0.1∼10Hz時の入力換算電圧ノイズ(G=10) 図15. 正電源PSRRの周波数特性(RTI) 18 0 2 4 6 8 10 12 14 16 1 10 100 1000 10000 100000 3 1 0-8 8 2 6 0 ) z H / A p( E SI O N T N E R R U C FREQUENCY (Hz) 150 130 110 90 70 50 30 10 1 10 100 1k 10k 100k 1M ) B d( R R S P FREQUENCY (Hz) G = 10 G = 5 G = 2 G = 1 7 1 0-8 8 2 6 0 図13. 電流ノイズ・スペクトル密度の周波数特性 図16. 負電源PSRRの周波数特性(RTI) 04 1 0-8 8 2 6 1s/DIV 140pA/DIV 15 10 5 0 –5 –10 –15 –40 –25 –10 5 20 35 50 65 80 85 110 125 IB– IB+ IOS ) A n( T N E R R U C S AI B TEMPERATURE (°C) 9 1 0-8 8 2 6 0 図14. 0.1∼10Hz時の電流ノイズ 図17. 入力バイアス電流とオフセット電流の温度特性

140 120 100 80 60 40 20 1 10 100 1k 10k 100k 1M ) B d( R R M C FREQUENCY (Hz) G = 10 G = 5 G = 2 G = 1 0 2 0-8 8 2 6 0 図18. CMRRの周波数特性 25 –10 –5 0 5 10 15 20 1k 10k 100k 1M 10M 100M ) B d( NI A G FREQUENCY (Hz) G = 10 G = 5 G = 2 G = 1 3 2 0-8 8 2 6 0 図21. ゲインの周波数特性 4 3 2 1 –1 –3 0 –2 –4 –10 –8 –6 –4 –2 0 2 4 6 8 10 4 2 0-8 8 2 6 0 ) VI D/ m p p 0 1( Y TI R A E NI L N O N OUTPUT VOLTAGE (V) f = 1kHz 140 120 100 80 60 40 20 1 10 100 1k 10k 100k 1M ) B d( R R M C FREQUENCY (Hz) G = 10 G = 5 G = 2 G = 1 1 2 0-8 8 2 6 0 図19. CMRRの周波数特性(1kΩ信号源不平衡) 図22. ゲイン非直線性(G=1、RL=10kΩ、2kΩ、600Ω) 10 –10 –8 –6 –4 –2 0 2 4 6 8 –50 –30 –10 10 30 50 70 90 110 130 9 4 0-8 8 2 6 0 ∆ ) V/ V µ( R R M C TEMPERATURE (°C) 4 3 2 1 –1 –3 0 –2 –4 –10 –8 –6 –4 –2 0 2 4 6 8 10 5 2 0-8 8 2 6 0 ) VI D/ m p p 0 1( Y TI R A E NI L N O N OUTPUT VOLTAGE (V) f = 1kHz 図20. CMRRの温度特性(G=1) 図23. ゲイン非直線性(G=2、RL=10kΩ、2kΩ、600Ω)

4 3 2 1 –1 –3 0 –2 –4 –10 –8 –6 –4 –2 0 2 4 6 8 10 7 2 0-8 8 2 6 0 ) VI D/ m p p 0 1( Y TI R A E NI L N O N OUTPUT VOLTAGE (V) f = 1kHz +VS –VS +1 +2 –2 –1 4 6 8 10 12 14 16 –40°C –40°C +25°C +25°C +85°C +85°C +125°C O T D E R E F F E R E G A T L O V T U P NI ) V( S E G A T L O V Y L P P U S SUPPLY VOLTAGE (±VS) +125°C 0 3 0-8 8 2 6 0 図25. ゲイン非直線性(G=1、RL=10kΩ、2kΩ、600Ω) 図28. 電源電圧 対 入力電圧限界値 (G=1、VREF=0V、RL=10kΩ) 16 –16 –12 –8 –4 0 4 8 12 –16 –12 –8 –4 0 4 8 12 16 ) V( E G A T L O V E D O M-N O M M O C T U P NI OUTPUT VOLTAGE (V) VS = ±15V –13.8V, +6.9V –13.8V, –6.9V +13.8V, –6.9V +13.8V, +6.9V –3.8V, +1.9V –3.8V, –1.9V +3.9V, +1.9V 0V, +3.7V 0V, –4.0V +3.8V, –2.1V 0V, +13.8V 0V, –14V VS = ±5V 8 2 0-8 8 2 6 0 15 –10 –5 –5 0 5 10 –16 –12 –8 –4 0 4 8 12 16 +VS +IN –IN –VS ) A m( T N E R R U C

DIFFERENTIAL INPUT VOLTAGE (V)

1 3 0-8 8 2 6 0 図26. 出力電圧 対 入力同相電圧範囲(G=1) 図29. 入力電圧 対 故障電流(G=10、RL=10kΩ) 4 3 2 1 –1 –3 0 –2 –4 –10 –8 –6 –4 –2 0 2 4 6 8 10 6 2 0-8 8 2 6 0 ) VI D/ m p p 0 1( Y TI R A E NI L N O N OUTPUT VOLTAGE (V) f = 1kHz 図24. ゲイン非直線性(G=5、RL=10kΩ、2kΩ、600Ω) 16 –16 –12 –8 –4 0 4 8 12 –16 –12 –8 –4 0 4 8 12 16 ) V( E G A T L O V E D O M-N O M M O C T U P NI OUTPUT VOLTAGE (V) VS = ±15V –14.1V, +13.6V –4.2V, +2.2V +4.3V, +2.1V +4.3V, –2.1V –4.2V, –2.0V 0V, –4.1V +0V, +3.5V 0V, –14V 0V, +13.8V –14.1V, –13.6V +13.6V, +13.1V +13.6V, –13.1V VS = ±5V 9 2 0-8 8 2 6 0 図27. 出力電圧 対 入力同相電圧範囲(G=10)

+VS –VS +0.2 +0.4 +0.6 +0.8 +1.0 –1.0 –0.8 –0.6 –0.4 –0.2 4 6 8 10 12 14 16 D E R E F F E R G NI W S E G A T L O V T U P T U O ) V( S E G A T L O V Y L P P U S O T SUPPLY VOLTAGE (±VS) –40°C –40°C +25°C +25°C +85°C +85°C +125°C +125°C 2 3 0-8 8 2 6 0 +VS –0.8 –0.4 –2.0 –1.6 –1.2 +1.2 +1.6 +2.0 +0.8 +0.4 –VS 0 2 4 6 8 10 12 14 16 5 3 0-8 8 2 6 0 D E R R E F E R G NI W S E G A T L O V T U P T U O ) V( S E G A T L O V Y L P P U S O T

OUTPUT CURRENT (mA) +125°C +85°C +25°C –40°C +125°C +85°C +25°C –40°C 図30. 電源電圧 対 出力電圧振幅(G=10、RL=2kΩ) 図33. 出力電流 対 出力電圧振幅 +VS –VS +0.2 +0.4 +0.6 +0.8 +1.0 –1.0 –0.8 –0.6 –0.4 –0.2 4 6 8 10 12 14 16 D E R E F F E R G NI W S E G A T L O V T U P T U O ) V( S E G A T L O V Y L P P U S O T SUPPLY VOLTAGE (±VS) –40°C +25°C +25°C +85°C +85°C +125°C +125°C –40°C 3 3 0-8 8 2 6 0 V T U O ) V( TIME (µs) 2µs/DIV 20mV/DIV NO LOAD 47pF 100pF 6 3 0-8 8 2 6 0 図31. 電源電圧 対 出力電圧振幅(G=10、RL=10kΩ) 図34. 各種容量負荷の小信号パルス応答 15 10 5 0 –5 –10 –15 100 1k 10k ) V( G NI W S E G A T L O V T U P T U O LOAD RSISTANCE (Ω ) +125°C –40°C –40°C +85°C +85°C +25°C +25°C +125°C 4 3 0-8 8 2 6 0 7 3 0-8 8 2 6 0 5V/DIV 2µs/DIV TIME (µs) 0.002%/DIV 585ns TO 0.01% 615ns TO 0.001% 図32. 負荷抵抗 対 出力電圧振幅 図35. 大信号パルス応答とセトリング時間 (G=1、RL=10kΩ)

8 3 0-8 8 2 6 0 5V/DIV 2µs/DIV TIME (µs) 0.002%/DIV 605ns TO 0.01% 635ns TO 0.001% V T U O ) V( TIME (µs) 2µs/DIV 20mV/DIV 24 0-8 8 2 6 0 図36. 大信号パルス応答とセトリング時間 (G=2、RL=10kΩ) 図39. 小信号応答(G=1、RL=2kΩ、CL=100pF) 9 3 0-8 8 2 6 0 5V/DIV 2µs/DIV TIME (µs) 0.002%/DIV 605ns TO 0.01% 635ns TO 0.001% V T U O ) V( TIME (µs) 2µs/DIV 20mV/DIV 3 4 0-8 8 2 6 0 図37. 大信号パルス応答とセトリング時間 (G=5、RL=10kΩ) 図40. 小信号応答(G=2、RL=2kΩ、CL=100pF) 0 4 0-8 8 2 6 0 5V/DIV 2µs/DIV TIME (µs) 0.002%/DIV 648ns TO 0.01% 685ns TO 0.001% V T U O ) V( TIME (µs) 2µs/DIV 20mV/DIV 4 4 0-8 8 2 6 0 図38. 大信号パルス応答とセトリング時間 (G=10、RL=10kΩ) 図41. 小信号応答(G=5、RL=2kΩ、CL=100pF)

V T U O ) V( TIME (µs) 2µs/DIV 20mV/DIV 54 0-8 8 2 6 0 1200 1000 800 600 400 200 0 2 4 6 8 10 12 14 16 18 20 0 5 0-8 8 2 6 0 ) s n( E MI T STEP SIZE (V) SETTLED TO 0.001% SETTLED TO 0.01% 図42. 小信号応答(G=10、RL=2kΩ、CL=100pF) 図45. ステップ・サイズ 対 セトリング時間 (G=5、RL=10kΩ) 1200 1000 800 600 400 200 0 2 4 6 8 10 12 14 16 18 20 8 4 0-8 8 2 6 0 ) s n( E MI T STEP SIZE (V) SETTLED TO 0.001% SETTLED TO 0.01% 1200 1000 800 600 400 200 0 2 4 6 8 10 12 14 16 18 20 6 4 0-8 8 2 6 0 ) s n( E MI T STEP SIZE (V) SETTLED TO 0.001% SETTLED TO 0.01% 図43. ステップ・サイズ 対 セトリング時間 (G=1、RL=10kΩ) 図46. ステップ・サイズ 対 セトリング時間 (G=10、RL=10kΩ) 1200 1000 800 600 400 200 0 2 4 6 8 10 12 14 16 18 20 7 4 0-8 8 2 6 0 ) s n( E MI T STEP SIZE (V) SETTLED TO 0.001% SETTLED TO 0.01% 図44. ステップ・サイズ 対 セトリング時間 (G=2、RL=10kΩ)

動作原理

図47. 簡略回路図 10kΩ 10kΩ 10kΩ 10kΩ REF OUTPUT A3 –IN +IN WR 2.2kΩ 2.2kΩ +VS +VS –VS –VS +VS –VS +VS –VS A1 A0 2.2kΩ DGND A1 A2 DIGITAL GAIN CONTROL 2.2kΩ +VS –VS +VS –VS +VS –VS +VS –VS 04 5 0-8 8 2 6 AD8250は従来型の3オペアンプ構成を採用したモノリシック計 装アンプです(図47)。本製品は、高精度、直線性性能、堅牢 なデジタル・インターフェースを可能とするアナログ・デバイ セズ独自のiCMOSプロセスで製造されています。パラレル・ インターフェースにより、1、2、5、10倍のゲイン設定を行う ことができます。ゲインは、内部の高精度抵抗アレイ内の抵抗 を切り替えて制御します(図47)。AD8250は電圧帰還回路を 備えていますが、ゲイン帯域幅積はゲイン1、2、5に対して増 加します。 これは、各ゲインでそれぞれ別々の周波数補償が行 われるためです。これにより、高いゲインで、帯域幅を最大に しています。 すべての内部アンプは、歪みキャンセル回路を使って高直線性 と超低THDを達成しています。レーザートリムされた薄膜抵抗 により、G=1で0.03%未満の最大ゲイン誤差、G=10で98dB の最小CMRRを実現しています。ピン配置は全周波数範囲で高 CMRRを可能にするよう最適化されているため、50kHzで最小 80dB(G=1)のCMRRを可能にしています。バランスのとれ た入力により、これまでCMRR性能に悪影響を与えていた寄生 を減少させています。ゲインの選択

ここでは、AD8250の基本動作の設定方法について説明します。 ロジック・ローとロジック・ハイの電圧規定値は「仕様」に記 載します。ロジック・ローの代表値は0V、ロジック・ハイは 5Vであり、 両電圧ともDGNDを基準に測定されます。DGND の許容電圧範囲については、表2の仕様を参照してください。 AD8250のゲインは、次の2つの方法で設定できます。 トランスペアレント・ゲイン・モード ゲインを設定する最も簡単な方法は、A0およびA1に入力され るロジック・ハイ電圧またはロジック・ロー電圧によって直接 ゲインを設定する方法です。図48は、トランスペアレント・ゲ イン・モード(このデータシートではすべてのこの名前で統一) によるゲイン設定方法の1例です。WR ___ を負電源に接続すると トランスペアレント・ゲイン・モードになります。このモード では、A0およびA1に入力する電圧をロジック・ローからロ ジック・ハイ(またはその逆)に変化させると、ゲインが直ち に変わります。表5にこのモードの真理値表を、図48にこの モードに設定されたAD8250を、それぞれ示します。 +15V –15V –15V A0 A1 WR +IN +5V +5V –IN 10µF 0.1µF 10µF 0.1µF G = 10 DGND DGND REF AD8250 5 5 0-06288 NOTE:1. IN TRANSPARENT GAIN MODE, WR IS TIED TO −VS. THE VOLTAGE LEVELS ON A0 AND A1 DETERMINE THE GAIN. IN THIS EXAMPLE, BOTH A0 AND A1 ARE SET TO LOGIC HIGH, RESULTING IN A GAIN OF 10.

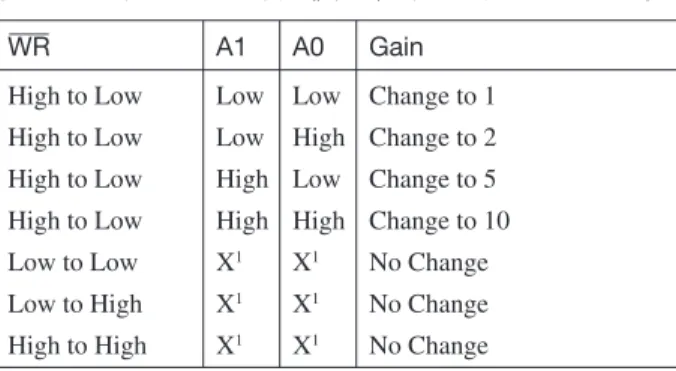

表5. ロジック・レベル真理値表 (トランスペアレント・ゲイン・モード) WR___ A1 A0 Gain –VS Low Low 1 –VS Low High 2 –VS High Low 5 –VS High High 10 ラッチ・ゲイン・モード アプリケーションには、同じPCB上にマルチプレクサ/その他 のプログラマブル・ゲイン計装アンプなど、複数のデバイスを 備えているものがあります。このような場合、デバイスはデー タ・バスを共有できます。AD8250のゲインはラッチ機能を持 つWR ___ を使って設定できるため、他のデバイスはA0とA1を共 用できます。図49に、この方法を使用する回路図、すなわち ラッチ・ゲイン・モードを示します。AD8250がこのモードに なるのは、WR ___ がロジック・ハイ(代表値5V)またはロジッ ク・ロー(代表値0V)に保持されているときです。A0とA1の 電圧は、WR ___ 信号がロジック・ハイからロジック・ローに変化 するときの立下がりエッジで読み出されます。これによってA0 とA1のロジック・レベルがラッチ入力され、ゲインが変更され ます。このゲインの変更については、表6の真理値表を参照し てください。 図49. ラッチ・ゲイン・モード(G=10) 表6. ロジック・レベル真理値表(ラッチ・ゲイン・モード) WR___ A1 A0 Gain High to Low Low Low Change to 1 High to Low Low High Change to 2 High to Low High Low Change to 5 High to Low High High Change to 10 Low to Low X1 X1 No Change

Low to High X1 X1 No Change

High to High X1 X1 No Change

1X=ドント・ケア パワーアップ時にAD8250がラッチ・ゲイン・モードになった と き は 、 デ フ ォ ル ト の ゲ イ ン 値1が 使 用 さ れ ま す 。 一 方 、 AD8250 がトランスペアレント・ゲイン・モードに設定されて いるときは、パワーアップ時にA0とA1の電圧レベルで選択さ れたゲインが使用されます。 ラッチ・ゲイン・モードのタイミング ラッチ・ゲイン・モードの場合は、WR ___ の立下がりエッジで ゲ インをラッチ入力する前の最小セットアップ時間(tSU)の間、 A0とA1のロジック・レベルを保持します。同様に、WR ___ の立 下がりエッジ後の最小ホールド時間(tHD)の間もそのロジッ ク・レベルを保持して、ゲインが正しくラッチ入力されるよう にします。tHD後に A0とA1でロジック・レベルを変更しても、 WR ___ の次の立下がりエッジまでゲインは変わりません。WR ___ が ハイレベルを維持できる最小時間はtWR__-HIGHで、WR ___ がローレベ ルを維持できる最小時間はtWR__-LOWです。表2に、デジタル・タ イミング仕様を示します。アンプのセトリング時間は、ゲイン 変更に必要な時間より長くなります。図50にタイミング図を示 します。 データ・バスを他のデバイスと共有する場合には、これらのデ バイスに入力されるロジック・レベルがAD8250の出力に混入 する可能性があります。混入は、ロジック信号のエッジ・レー トを下げて最小限に抑えることができます。また、PCBの優れ たレイアウトにより、ボードのデジタル部とアナログ部との結 合を削減することもできます。 +15V –15V A0 A1 WR +IN –IN 10µF 0.1µF 10µF 0.1µF DGND DGND REF AD8250 A0 A1 WR +5V +5V +5V 0V 0V 0V G = PREVIOUS STATE G = 10 6 5 0-8 8 2 6 0 + – NOTE:

1. ON THE DOWNWARD EDGE OF WR, AS IT TRANSITIONS FROM LOGIC HIGH TO LOGIC LOW, THE VOLTAGES ON A0 AND A1 ARE READ AND LATCHED IN, RESULTING IN A

GAIN CHANGE. IN THIS EXAMPLE, THE GAIN SWITCHES TO G = 10.

図50. ラッチ・ゲイン・モードのタイミング図 A0, A1 WR tSU tHD tWR-HIGH tWR-LOW 0 7 5 0-8 8 2 6

電源レギュレーションとバイパス

AD8250は高いPSRRを備えていますが、最適な性能を達成す るには、安定したDC電圧で計装アンプに電源を供給する必要 があります。電源ピンのノイズは性能に悪影響を与えることが あります。すべてのリニア回路の場合と同様、バイパス・コン デンサを使ってアンプをデカップリングします。 0.1µFのコンデンサは、各電源ピンの近くに接続します。10µF のタンタル・コンデンサはデバイスから離れたところに接続で きます(図51を参照)。多くの場合、これらのコンデンサは他 の高精度ICと共用できます。 図51. 電源デカップリング(REFと出力はグラウンドを基準)入力バイアス電流のリターン・パス

AD8250の入力バイアス電流には、ローカル・アナログ・グラ ウンドへのリターン・パスが必要です。熱電対のように信号源 がリターン電流パスを持っていない場合には、図52のように接 続します。 図52. IBIASパスの構成入力保護

AD8250のすべてのピンは、ESD保護されています。図47に示 すように、ESDダイオードの前に2.2kΩの直列抵抗が接続され ています。この抵抗によってダイオードに流れる電流が制限さ れるため、正電源の13V上、また負電源の13V下までのDC過負 荷状態が許容されています。各電源レールを超える13V以上の 電圧に対しては、各入力に直列に外付け抵抗を接続して電流を 制限します。いずれの場合でも、AD8250は室温で連続6mAの 電流を安全に処理できます。AD8250に非常に大きな過負荷電 圧が入力されるアプリケーションでは、外付け直列抵抗と、 BAV199L、FJH1100、SP720のような低リーク・ダイオー ド・クランプを使う必要があります。 THERMOCOUPLE +VS REF –VS AD8250 CAPACITIVELY COUPLED +VS REF C C –VS AD8250 TRANSFORMER +VS REF –VS AD8250 INCORRECT CAPACITIVELY COUPLED +VS REF C R R C –VS AD8250 1 fHIGH-PASS =2πRC THERMOCOUPLE +VS REF –VS 10MΩ AD8250 TRANSFORMER +VS REF –VS AD8250 CORRECT 9 5 0-8 8 2 6 0 AD8250 +VS +IN –IN LOAD REF 0.1µF 10µF 0.1µF 10µF –VS DGND VOUT DGND A0 A1 WR 8 5 0-8 8 2 6 0リファレンス・ピン

リファレンス・ピン(REF)には10kΩの抵抗を接続します (図47を参照)。計装アンプの出力は、REFピンの電圧を基準に しています。これは、出力信号をローカル・アナログ・グラウ ンド以外の電圧にオフセットさせる場合に便利です。たとえば、 AD8250が単電源ADCとインターフェースできるように、電圧 源をREFピンに接続して出力をレベル・シフトさせることがで きます。許容リファレンス電圧範囲は、ゲイン、同相入力、電 源電圧の関数になります。REFピンは、+VSまたは−VSを 0.5V以上超えることはできません。 最適な性能を得るためには、特に出力がREFピンを基準に測定 されない場合はREFピンへのソース・インピーダンスを小さく 維持して、寄生抵抗がCMRRとゲイン精度に悪影響を与えない ようにします。 図53. リファレンス・ピンの駆動同相入力電圧範囲

3オペアンプ構成のAD8250では、増幅後に同相電圧を除去しま す。したがって、AD8250の内部ノードでは増幅信号と同相信 号の組み合わせが生じます。これらの組み合わせ信号は、入力 信号や出力信号で制限されないときでも、電源電圧で制限する ことができます。図26と図27に、各種の出力電圧、電源電圧、 ゲインに対する許容同相入力電圧範囲を示します。レイアウト

グラウンディング ミックスド・シグナル回路では、低レベルのアナログ信号をノ イ ズ の 多 い デ ジ タ ル 環 境 か ら 分 離 す る 必 要 が あ り ま す 。 AD8250を使用するデザインも例外ではありません。このデバ イスの電源電圧は、アナログ・グラウンドを基準とし、デジタ ル回路はデジタル・グラウンドを基準とします。両グラウンド を1つのグラウンド・プレーンに接続することは便利ですが、 グラウンド配線とPCボードを流れる電流が大きな誤差を発生さ せることがあります。このため、アナログとデジタルのグラウ ンド・プレーンは別々に使用します。アナログ・グラウンドと デジタル・グラウンドの接続は、グラウンド・ポイントの1箇 所でのみ行いスター結線にしてください。 AD8250の出力電圧は、リファレンス・ピンの電位を基準にし ています。REFは適切なローカル・アナログ・グラウンドに接 続するか、ローカル・アナログ・グラウンドを基準とする電圧 に接続するようにしてください。 カップリング・ノイズ 次のガイドラインに従って、AD8250へのカップリング・ノイ ズを防止します。 • デジタル・ラインがデバイスの真下を通らないようにしま す。 • アナログ・グラウンド・プレーンはAD8250の下を通しま す。 • ボードの他の部分へのノイズの拡散を防ぐため、高速ス イッチング信号はデジタル・グラウンドでシールドして、 アナログ信号パスの近くを通らないようにします。 • デジタル信号とアナログ信号が交差しないようにします。 • 電源ラインはできるだけ太いパターンにして、低インピー ダンス・パスとなるようにします。必要なデカップリング については、「電源レギュレーションとバイパス」のガイド ラインに従ってください。 同相ノイズ除去 全周波数範囲で高いCMRRを持つAD8250は、電源ノイズとそ の高調波のような外乱に対する耐性が、一般的な計装アンプ (200HzでCMRRが低下する)より優れています。これらの計 装アンプは、多くの場合、この不足を補償するために入力側に コモン・モード・フィルタを必要とします。しかし、AD8250 は広い周波数範囲でCMRRを阻止できるため、フィルタは不要 になります。 適切なボード・レイアウトを行えばシステム性能を最大化でき ます。周波数全体で高いCMRRを維持するためには、入力パ ターンを対称に配置します。このパターンでは、抵抗や容量の バランスを維持します。これは、入力ピンおよびパターンの下 に位置する他のPCBメタル層にも当てはまります。さらに、 ソース抵抗と容量は可能な限り入力の近くに配置しておきま す。パターンが他の層からの入力と交差する場合は、入力パ ターンに対して直角に配線します。RF

干渉

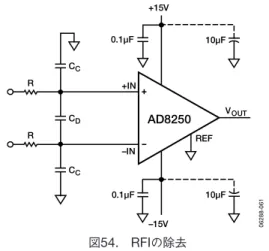

強いRF信号が存在するアプリケーションでアンプを使用する と、多くの場合、RF整流の問題が生じます。これらの外乱は小 さいDCオフセット電圧として現れることがあります。高周波 信号は、図54に示すように計装アンプの入力に接続されたロー パスR-C回路で除去できます。このフィルタは、次式に従って 入力信号の帯域幅を制限します。 ここで、CD≧10CC ) 2πR 1 C D DIFF FilterFreq + = C CM FilterFreq 2πRC 1 = (2C C INCORRECT AD8250 VREF CORRECT AD8250 OP1177 + – VREF 0 0 6 0-8 8 2 6図54. RFIの除去 RとCCの値は、RFIを最小化するように選択します。正側入力 のR×CCと負側入力のR×CCとの不一致は、AD8250のCMRR の性能を低下させます。CCの値より10倍大きいCDの値を使う と、不一致の影響は小さくなるため、性能が改善されます。

A/D

コンバータの駆動

計装アンプは、優れたCMRRが可能であるためにA/Dコンバー タの前に使用されることがよくあります。一般に、計装アンプ はADCを駆動するためのバッファを必要とします。しかし、低 出 力 ノ イ ズ 、 低 歪 み 、 短 い セ ト リ ン グ 時 間 の 特 性 を 持 つ AD8250は優れたADCドライバとして機能します。 下図の例では、1nFのコンデンサと49.9Ωの抵抗がAD7612用の 折り返し防止フィルタとして機能します。また、1nFのコンデ ンサは、ADCのスイッチド・キャパシタ入力に必要な電荷を保 存/供給する働きもあります。49.9Ωの直列抵抗はアンプから の1nF負荷の負担を減らし、AD7612のスイッチド・キャパシタ 入力から流出するキックバック電流がアンプに流れないように します。小さい抵抗を選択すると、A D 8 2 5 0の出力電圧と AD7612の入力電圧との相関を良くすることができますが、 AD8250が不安定になることがあります。精度を維持するため に小さい抵抗を使用するか、安定性を維持するために大きな抵 抗を使用するかは適正に選択する必要があります。 図55. ADCの駆動 0.1µF 0.1µF 1nF 49.9Ω AD7612 ADR435 +12V –12V +5V +15V –15V A0 A1 WR +IN –IN 10µF 0.1µF 10µF 0.1µF REF AD8250 2 6 0-8 8 2 6 0 DGND DGND R R AD8250 +15V +IN –IN 0.1µF 10µF 10µF 0.1µF REF VOUT –15V CD CC CC 01 6 0-8 8 2 6アプリケーション

差動出力

アプリケーションによっては、差動信号の発生が必要となりま す。多くの場合、高分解能ADCは差動入力を必要とします。ま た、長距離伝送で干渉の影響を少なくするために差動信号が必 要になる場合もあります。 図57に、差動信号を出力するAD8250の構成方法を示します。 オペアンプAD817は、差動電圧を発生するために反転回路とし て使用します。VREFは、図中の計算式に従って出力の中点を設 定します。オペアンプからの誤差は両出力に共通であるため同 相です。同様に、不一致抵抗使用による誤差により、同相DC オフセット誤差が発生します。このような誤差は、差動入力 ADCまたは計装アンプによる差動信号処理で除去されます。 この回路を使用して差動ADCを駆動する場合は、ADCのリ ファレンスから抵抗分圧器を使用してVREFを設定することによ り、出力をADCとレシオメトリックにできます。マイクロコントローラによるゲインの設定

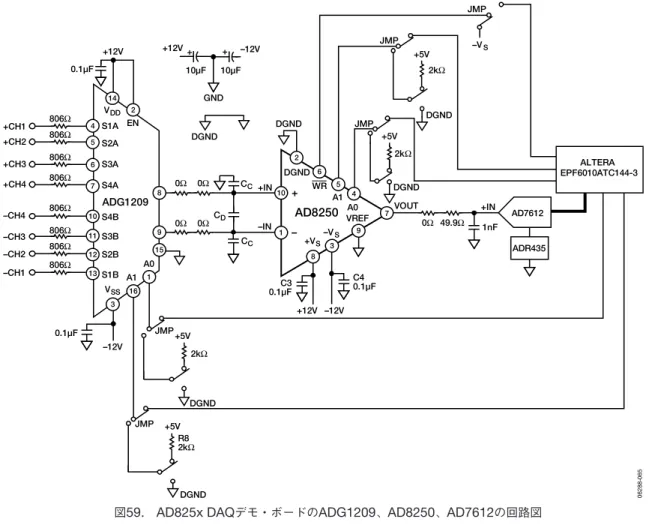

図56. マイクロコントローラを使用したゲインの設定 +15V MICRO-CONTROLLER –15V A0 A1 WR +IN –IN 10µF 0.1µF 10µF 0.1µF REF AD8250 3 6 0-8 8 2 6 0 + – DGND DGND 図33. レベル・シフトによる差動出力 +12V –12V A0 A1 WR +IN 10µF 0.1µF 10µF 0.1µF AD8250 REF G = 1 0.1µF 4.99kΩ 4.99kΩ AD817 0.1µF +12V –12V VREF 0V VOUTA = VIN + VREF 2 2 VOUTB = –VIN + VREF +2.5V –2.5V 0V +2.5V –2.5V0V TIME AMPLITUDE TIME AMPLITUDE +5V –5V AMPLITUDE 10pF +12V –12V VIN 4 6 0-8 8 2 6 0 + – + – DGND DGND図59. AD825x DAQデモ・ボードのADG1209、AD8250、AD7612の回路図 5 6 0-8 8 2 6 0 AD8250 2 +IN –IN A1 A0 VOUT VREF –VS +VS DGND 5 3 4 9 1 7 10 11 12 13 14 15 16 6 2 S1A EN S2A S3A S4A S1B S2B S3B S4B A0 A1 VSS VDD JMP JMP JMP +12V –12V +12V –12V JMP JMP –VS +5V +5V DGND 806Ω 806Ω 806Ω 806Ω 806Ω 806Ω 806Ω 806Ω 0Ω 0Ω 49.9Ω 0Ω –CH1 +CH1 +CH2 –CH2 +CH3 –CH3 +CH4 –CH4 1nF 2kΩ 2kΩ 0.1µF GND +12V+ + –12V 10µF 10µF 0.1µF CD CC CC C3 0.1µF C4 0.1µF +5V +5V DGND DGND R8 2kΩ +IN AD7612 ADR435 ADG1209 DGND ALTERA EPF6010ATC144-3 8 0Ω 0Ω 1 10 6 WR 9 4 5 8 3 7 + – DGND 2kΩ DGND

データ・アクイジション

AD8250は、優れた計装アンプとしてデータ・アクイジショ ン・システムで力を発揮します。このデバイスは広帯域幅、低 歪み、短いセトリング時間の特性を持っているため、各種16 ビットADCの信号コンディショニングを行うことができます。 図59に、デモ用のAD825xデータ・アクイジション・ボードの 回路図を示します。高速スルーレートのAD8250により、マル チプレクサ入力からの急激に変化する信号に対してコンディ シ ョ ニ ン グ を 行 う こ と が で き ま す 。F P G Aは 、A D 7 6 1 2、 AD8250、ADG1209を制御します。また、トランスペアレン ト・ゲイン・モードのときは、機械的スイッチやジャンパ線を 使ってゲインをピン設定することができます。 このシステムは、テスト中に1kHzで−111dBのTHD、91dBの S/N比を達成しています(図58を参照)。図58. AD8250を使用したAD825x DAQデモ・ボードのFFT

(1kHz信号) 0 –140 –130 –120 –110 –100 –90 –80 –70 –60 –50 –40 –30 –20 –10 0 5 10 15 20 25 30 35 40 45 50 ) B d( E D U TI L P M A FREQUENCY (kHz) 6 6 0-8 8 2 6 0

D06288-0-1/07(0)-J

外形寸法

図60. 10ピン・ミニ・スモール・アウトライン・パッケージ[MSOP] (RM-10) 寸法単位:mmオーダー・ガイド

Model Temperature Range Package Description Package Option Branding AD8250ARMZ1 – 40℃to +85℃ 10-Lead MSOP RM-10 H00

AD8250ARMZ-RL1 – 40℃to +85℃ 10-Lead MSOP RM-10 H00

AD8250ARMZ-R71 – 40℃to +85℃ 10-Lead MSOP RM-10 H00

AD8250-EVALZ1 Evaluation Board

1 Z=鉛フリー製品

COMPLIANT TO JEDEC STANDARDS MO-187-BA 0.23 0.08 0.80 0.60 0.40 8° 0° 0.15 0.05 0.33 0.17 0.95 0.85 0.75 SEATING PLANE 1.10 MAX 10 6 5 1 0.50 BSC PIN 1 COPLANARITY 0.10 3.10 3.00 2.90 3.10 3.00 2.90 5.15 4.90 4.65