R 本資料は英語版 (v1.2) を翻訳 し た も のです。英語の更新バー ジ ョ ンが リ リ ース さ れている場合には、 最新の英語版を必ず ご参照 く だ さ い。

XtremeDSP DSP48A

ユーザー

ガ イ ド

UG431 (v1.2) 2007 年 11 月 5 日Xilinx is disclosing this user guide, manual, release note, and/or specification (the “Documentation”) to you solely for use in the development of designs to operate with Xilinx hardware devices. You may not reproduce, distribute, republish, download, display, post, or transmit the Documentation in any form or by any means including, but not limited to, electronic, mechanical, photocopying, recording, or otherwise, without the prior written consent of Xilinx. Xilinx expressly disclaims any liability arising out of your use of the Documentation. Xilinx reserves the right, at its sole discretion, to change the Documentation without notice at any time. Xilinx assumes no obligation to correct any errors contained in the Documentation, or to advise you of any corrections or updates. Xilinx expressly disclaims any liability in connection with technical support or assistance that may be provided to you in connection with the Information.

THE DOCUMENTATION IS DISCLOSED TO YOU “AS-IS” WITH NO WARRANTY OF ANY KIND. XILINX MAKES NO OTHER WARRANTIES, WHETHER EXPRESS, IMPLIED, OR STATUTORY, REGARDING THE DOCUMENTATION, INCLUDING ANY WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NONINFRINGEMENT OF THIRD-PARTY RIGHTS. IN NO EVENT WILL XILINX BE LIABLE FOR ANY CONSEQUENTIAL, INDIRECT, EXEMPLARY, SPECIAL, OR INCIDENTAL DAMAGES, INCLUDING ANY LOSS OF DATA OR LOST PROFITS, ARISING FROM YOUR USE OF THE DOCUMENTATION.

© 2007 Xilinx, Inc. All rights reserved.

XILINX, the Xilinx logo, the Brand Window, and other designated brands included herein are trademarks of Xilinx, Inc. All other trademarks are the property of their respective owners.

改定履歴

次の表に、 こ の文書の改定履歴を示 し ます。 日付 バージ ョ ン 改定履歴 2007/04/02 1.0 初版 リ リ ース 2007/05/29 1.1 第 2 章の タ イ ト ル と 図を変更 2007/11/05 1.2 • 図 1-1:XC3SD1800A

デバ イ ス の新 し い DSP48A 配置図を追加 • 図 1-2 :XC3SD3400A

デバ イ ス の新 し い DSP48A 配置図を追加 • 表 1-2 : 信号 B お よ び BCIN の機能の説明を変更 • 図 1-5 : 図の下に メ モ 9 を追加 • 図 1-8 : B1 レ ジ ス タ の EN ピ ンに CEB ピ ン を接続 • 表 1-8 : 48 ビ ッ ト 加算/減算器のシ リ コ ン使用率を 1 DSP ス ラ イ ス に変更 • 第 1 章 : 微修正 • 「VHDL お よ び Verilog の イ ン ス タ ン シエーシ ョ ンテ ンプ レー ト 」 を更新図一覧

. . . 5表一覧

. . . 7本ユーザー

ガ イ ド について

本ユーザーガ イ ド の内容 . . . 9 その他の資料 . . . 9 表記規則 . . . 9 書体 . . . 9 オン ラ イ ンマニ ュ アル . . . 10第

1

章

: XtremeDSP

のデザイ ンの考察

は じ めに . . . 11 アーキ テ ク チ ャ のハ イ ラ イ ト . . . 12 Spartan-3A DSP デバ イ ス別の DSP48A ス ラ イ ス数 . . . 13 DSP48A ス ラ イ ス のプ リ ミ テ ィ ブ . . . 16 OPMODE ピ ンの説明 . . . 19 DSP48A ス ラ イ ス の属性 . . . 19 VHDL お よ び Verilog の イ ン ス タ ン シエーシ ョ ンテ ンプ レー ト . . . 20 DSP48A ス ラ イ スお よ び イ ン タ ー コ ネ ク ト . . . 21 DSP48E ス ラ イ ス動作の概略 . . . 23 論理式 . . . 23 A、B、C、D、 お よ び P ポー ト ロ ジ ッ ク . . . 24 OPMODE ポー ト ロ ジ ッ ク . . . 26 2 の補数乗算器 . . . 27 X お よ び Z マルチプ レ ク サ . . . 27 前置加算/減算器 . . . 30 後置加算器/減算器/累算器 . . . 30 キ ャ リ ー入力 ロ ジ ッ ク . . . 30 大規模乗算器の実現 . . . 31 FIR フ ィ ル タ . . . 32 基本的な FIR フ ィ ル タ . . . 32 マルチチ ャ ネル FIR フ ィ ル タ . . . 33 FIR フ ィ ル タ の作成 . . . 33 加算器カ ス ケー ド お よ び加算器ツ リ ー . . . 34 DSP48A ス ラ イ ス の機能使用例 . . . 37 完全にパ イ プ ラ イ ン化 さ れた 35 x 35 乗算器使用例 . . . 37 完全にパ イ プ ラ イ ン化 さ れた 18 x 18 複素乗算器使用例 . . . 38 完全にパ イ プ ラ イ ン化 さ れた、18 x 18 複素 MACC 使用例 . . . 39 その他の機能使用例 . . . 4318 ビ ッ ト のシ フ ト 量可変循環バレルシ フ タ 使用例 . . . 43 追加情報 . . . 45

第

2

章

: DSP48A

前置加算器の使用

は じ めに . . . 47 対称型 FIR フ ィ ル タ . . . 47 対称型 FIR フ ィ ル タ イ ンプ リ メ ン テーシ ョ ン . . . 48 逆方向遅延カ ス ケー ド のパ イ プ ラ イ ン化 . . . 49 複素乗算器 . . . 51第

1

章

: XtremeDSP

のデザイ ンの考察

図 1-1 : XC3SD1800A FPGA の DSP48A の配置図 . . . 14

図 1-2 : XC3SD3400A FPGA の DSP48A の配置図 . . . 15

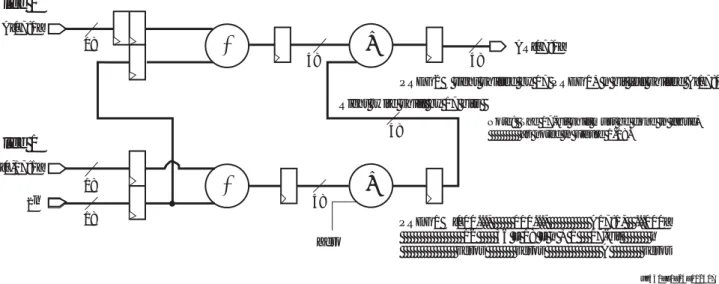

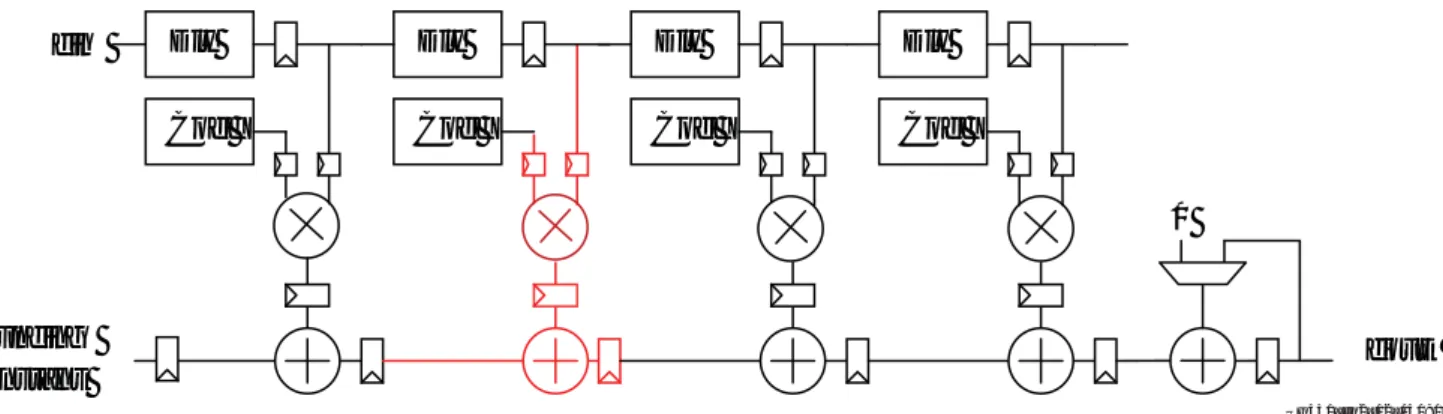

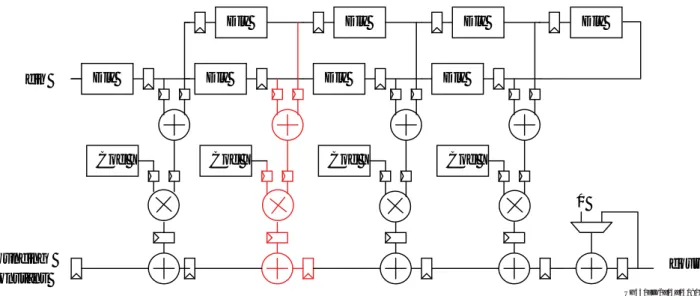

図 1-3 : DSP48A ス ラ イ ス のプ リ ミ テ ィ ブ . . . 16 図 1-4 : DSP48A の配置. . . 21 図 1-5 : DSP48A ス ラ イ ス. . . 22 図 1-6 : DSP48A ス ラ イ スの簡略図. . . 24 図 1-7 : A 入力 ロ ジ ッ ク. . . 25 図 1-8 : B お よ び D 入力 ロ ジ ッ ク . . . 25 図 1-9 : C 入力 ロ ジ ッ ク. . . 26 図 1-10 : P 出力 ロ ジ ッ ク . . . 26 図 1-11 : OPMODE ポー ト ロ ジ ッ ク . . . 26 図 1-12 : 2 の補数乗算器 と オプシ ョ ンの MREG . . . 27 図 1-13 : 後置加算/減算器に供給 さ れ る キ ャ リ ー入力 ロ ジ ッ ク . . . 31 図 1-14 : 18 x 18 ビ ッ ト の乗算器に よ っ て構成 さ れ る 35 x 35 ビ ッ ト 乗算 . . . 31 図 1-15 : 従来の タ ッ プ遅延 ラ イ ン FIR フ ィ ル タ . . . 33 図 1-16 : ソ フ ト ウ ェ ア指定の無線デジ タ ルダ ウ ン コ ンバー タ. . . 33 図 1-17 : DSP48A ス ラ イ ス を使用 し た FIR フ ィ ル タ 加算器ツ リ ー . . . 35 図 1-18 : 加算器カ ス ケー ド のシ ス ト リ ッ ク FIR. . . 36 図 1-19 : カ ス ケー ド 接続 さ れた DSP48A ス ラ イ ス か ら 構築 さ れたパ イ プ ラ イ ン化 さ れた 35x35 乗算器. . . 37 図 1-20 : カ ス ケー ド 接続 さ れた DSP48A ス ラ イ ス か ら 構築 さ れたパ イ プ ラ イ ン化 さ れていない 35 x 35 乗算器. . . 38 図 1-21 : パ イ プ ラ イ ン化 さ れた複雑な 18 x 18 乗算 . . . 39 図 1-22 : 完全にパ イ プ ラ イ ン化 さ れた 18 x 18 複素 MACC (最初の N サ イ ク ルの動作) . . . 40 図 1-23 : 完全にパ イ プ ラ イ ン化 さ れた 18 x 18 複素 MACC (最終サ イ ク ルま たは N+1 サ イ ク ルの動作). . . 41 図 1-24 : 完全にパ イ プ ラ イ ン化 さ れた複雑な 18 x 18 複素 MACC (追加ス ラ イ ス付 き) . . . 42 図 1-25 : 循環バレルシ フ タ の動作 . . . 43 図 1-26 : 動的な 18 ビ ッ ト のバレルシ フ タ. . . 44

第

2

章

: DSP48A

前置加算器の使用

図 2-1 : 前置加算器付 き DSP48A . . . 47 図 2-2 : 非対称型 FIR フ ィ ル タアーキ テ ク チ ャ の簡略図 . . . 48 図 2-3 : 基本的な偶数 タ ッ プの対称型 FIR フ ィ ル タ アーキテ ク チ ャ . . . 49 図 2-4 : 基本的な奇数 タ ッ プの対称型 FIR フ ィ ル タ アーキテ ク チ ャ . . . 49 図 2-5 : 反転パ イ プ ラ イ ンが除去 さ れた状態. . . 50 図 2-6 : キ ャ プチ ャ レ ジ ス タ の追加 . . . 50 図 2-7 : 4 つの乗算器に よ る 複素乗算器. . . 51 図 2-8 : 3 つの乗算器バージ ョ ン . . . 52 図 2-9 : 完全にパ イ プ ラ イ ン化 さ れたバージ ョ ン . . . 52第

1

章

: XtremeDSP

のデザイ ンの考察

表 1-1 : 各フ ァ ミ リ メ ンバの DSP48A ス ラ イ ス数. . . 13 表 1-2 : DSP48A ス ラ イ スポー ト の一覧お よ び説明 . . . 16 表 1-3 : OPMODE ピ ンの説明 . . . 19 表 1-4 : OPMODE 制御ビ ッ ト お よ び X マルチプ レ ク サ出力. . . 28 表 1-5 : OPMODE 制御ビ ッ ト お よ び Z マルチプ レ ク サ出力. . . 28 表 1-6 : OPMODE[7:4] の機能の説明 . . . 28 表 1-7 : DSP48A 動作モー ド. . . 29 表 1-8 : その他の機能使用例 . . . 43第

2

章

: DSP48A

前置加算器の使用

表 2-1 : 前置加算器付 き DSP48A . . . 47 表 2-2 : DSP48A の数式. . . 47本ユーザー

ガ イ ド について

本書では、Spartan™-3A DSP FPGA の XtremeDSP™ DSP48A ス ラ イ ス の機能について詳細に説

明 し ます。

本ユーザー

ガ イ ド の内容

本書では、 次の項目について説明 し ます。 • 第 1 章「XtremeDSP のデザ イ ンの考察」では、DSP48A ス ラ イ ス と その要素お よ びアプ リ ケー シ ョ ンについて説明 し ます。 • 第 2 章 「DSP48A 前置加算器の使用」では、 対称型 FIR フ ィ ル タ お よ び複素乗算器の集積度、 性能、 お よ び消費電力について説明 し ます。その他の資料

追加の資料は、 次のザ イ リ ン ク ス ウ ェ ブサ イ ト か ら ダ ウ ン ロ ー ド で き ます。 japan.xilinx.com/literature シ リ コ ンお よ び ソ フ ト ウ ェ アに関す る 情報やア ンサーデー タ ベー ス の検索、 ま たは ウ ェ ブケー ス を開 く 場合は、 次の ウ ェ ブサ イ ト か ら ア ク セ ス し て く だ さ い。 japan.xilinx.com/support表記規則

こ のマニ ュ アルでは、 次の表記規則を使用 し てい ます。各規則について、 例を挙げて説明 し ます。書体

次の規則は、 すべてのマニ ュ アルで使用 さ れてい ます。 表記規則 使用箇所 例 Courierフ ォ ン ト シ ス テ ムが表示す る メ ッ セージ、 プ ロ ンプ ト 、 プ ロ グ ラ ム フ ァ イ ルを表示 し ます。 speed grade: - 100 Courier フ ォ ン ト (太字) 構文内で入力す る コ マ ン ド を示 し ます。 ngdbuild design_name イ タ リ ッ ク フ ォ ン ト ユーザーが値を入力す る 必要の あ る 構文内の変数に使用 し ます。 ngdbuild design_nameオ ン ラ イ ン

マニ ュ アル

こ のマニ ュ アルでは、 次の規則が使用 さ れてい ます。 二重/一重かぎか っ こ 『』、 「」 『』 はマニ ュ アル名を、 「」 はセ ク シ ョ ン名を示 し ます。 詳細については、 『開発シ ス テ ム リ フ ァ レ ン ス ガ イ ド 』 の 「PAR」 を参照 し て く だ さ い。 角か っ こ [ ] オプシ ョ ンの入力ま たはパ ラ メ ー タ を示 し ますが、 bus[7:0] の よ う なバ ス仕様では必ず使用 し ます。 ま た、GUI 表記に も 使 用 し ます。 ngdbuild [option_name] design_name [File] → [Open] を ク リ ッ ク し ます。 中か っ こ { } 1 リ ス ト を示 し ます。つ以上の項目を選択す る ための lowpwr ={on|off} 縦棒 | 選択す る リ ス ト の項目を分離 します。 lowpwr ={on|off} 縦の省略記号 . . . 繰 り 返 し 項目が省略 さ れてい る こ と を示 し ます。IOB #1: Name = QOUT’ IOB #2: Name = CLKIN’

. . .

横の省略記号 . . . 繰 り 返 し 項目が省略 さ れてい るこ と を示 し ます。 allow block block_name loc1 loc2 ... locn;

表記規則 使用箇所 例 表記規則 使用箇所 例 青色の文字 マニ ュ アル内の相互参照を示 し ます。 詳 細 に つ い て は、「そ の 他 の リ ソ ース」 を参照 し て く だ さ い。 詳細については、 第 1 章の「 タ イ ト ルフ ォーマ ッ ト 」を参照 し て く だ さ い。 赤色の文字 ほかのマニ ュ アルへの相互参照 を示 し ます。 詳細については、 『Virtex-II Platform FPGA ユーザーガ イ ド 』 の図 2-5を参照 し て く だ さ い。 青色の下線付 き 文字 ウ ェ ブサ イ ト (URL) へのハ イ パー リ ン ク です。 最新の ス ピー ド フ ァ イ ルは、 http://japan.xilinx.comか ら 入手 で き ます。

第

1

章

XtremeDSP

のデザイ ンの考察

本章では、XtremeDSP™ の DSP (デジ タ ル信号処理) 要素、DSP48A ス ラ イ ス を技術的に詳細に説 明 し ます。

DSP48A ス ラ イ ス は、Spartan™-3A DSP FPGA フ ァ ミ リ に特有です。 各 XtremeDSP ス ラ イ ス は

DSP48A ス ラ イ ス を 1 つ含み、こ れに よ っ て自由度の高い DSP アーキ テ ク チ ャ を実現 し てい ます。 多 く の DSP デザ イ ンでは乗算後に加算が続 き ます。Spartan-3A DSP デバ イ ス では、 こ れ ら のエ レ メ ン ト が専用回路でサポー ト さ れてい ます。 DSP48A ス ラ イ ス は、 乗算器、 乗算累算器 (MACC)、 前置加算/減算器付 き の乗算累算器、 積和累 算器、 ワ イ ド バ スマルチプ レ ク サ、 マグ ニチ ュ ー ド コ ンパレー タ 、 ま たは多入力カ ウ ン タ な ど の 独立 し た機能を多数サポー ト し てい ます。 ま た、 こ のアーキ テ ク チ ャ は複数の DSP48A ス ラ イ ス の 接続を サポー ト し 、 汎用 FPGA フ ァ ブ リ ッ ク を使用す る こ と な く 、 多入力演算処理、DSP フ ィ ル タ 、 お よ び複素演算を実現 し ます。 すべての Spartan-3A DSP フ ァ ミ リ メ ンバで利用可能な DSP48A ス ラ イ ス は、 新 し い DSP アルゴ リ ズ ム と 、 従来の FPGA よ り も 高度な レベルの DSP の統合をサポー ト し ます。 汎用 FPGA フ ァ ブ リ ッ ク の利用を最小限に抑え る こ と で、 低消費電力、 高性能、 かつ効率的なシ リ コ ンの使用を実現 し ます。 本章は、 次のセ ク シ ョ ンで構成 さ れてい ます。 • 「は じ めに」 • 「アーキ テ ク チ ャ のハ イ ラ イ ト 」 • 「Spartan-3A DSP デバ イ ス別の DSP48A ス ラ イ ス数」 • 「DSP48A ス ラ イ スお よ び イ ン タ ー コ ネ ク ト 」 • 「DSP48E ス ラ イ ス動作の概略」 • 「A、B、C、D、 お よ び P ポー ト ロ ジ ッ ク 」 • 「大規模乗算器の実現」 • 「FIR フ ィ ル タ 」 • 「加算器カ ス ケー ド お よ び加算器ツ リ ー」 • 「DSP48A ス ラ イ ス の機能使用例」 • 「追加情報」

は じ めに

DSP48A ス ラ イ ス は、従来の FPGA と 比較 し て、 よ り 高度な DSP 機能を実現 し ます。DSP48A は、

Virtex™-4 DSP48 ス ラ イ ス か ら 派 生 し て い ま す (詳 細 は、UG073 : 『Virtex™-4 FPGA の

多 く の DSP アルゴ リ ズ ムでは、 汎用 FPGA フ ァ ブ リ ッ ク の利用を最小限に抑え ら れ、 低消費電力、 高性能、 かつ効率的なデバ イ ス の使用を実現で き ま す。 ま ず、DSP48A ス ラ イ ス には、18 ビ ッ ト の入力前置加算器が付いた 18 x 18 ビ ッ ト の 2 の補数乗算器お よ び 48 ビ ッ ト に符号拡張 さ れた乗 算器/減算器/累算器が含 ま れてい ます。 更に よ く 見 る と 、 演算構築ブ ロ ッ ク の有用性、 柔軟性、 お よ び速度を よ り 強化す る 細かい機能が数多 く 含まれてい る こ と がわか り ます。 入力オペ ラ ン ド 、 中 間積、 お よ び累算器出力のパ イ プ ラ イ ン はプ ロ グ ラ ム可能で、 ス ループ ッ ト を向上 さ せ ま す。48 ビ ッ ト の内部バス に よ っ て DSP ス ラ イ ス を実質的に無制限に接続可能です。 最 も 重要な機能の 1 つは、 フ ァ ブ リ ッ ク の汎用配線を使用せずに XtremeDSP ス ラ イ ス の出力を次 の ス ラ イ ス にカ ス ケー ド で き る こ と です。 こ のパ ス に よ っ て、 多 く の DSP フ ィ ル タ 機能で タ ッ プ の長 さ に関わ ら ず、 高性能、 低消費電力の積和を実現で き ます。 フ ィ ル タ 構築向けの も う 1 つの重 要な機能 と し て、 ス ラ イ ス間の一連の入力を カ ス ケー ド 接続す る 機能があ り ます。 C 入力ポー ト では、 前置加算器を後置加算器にカ ス ケー ド 接続 し た 3 入力加算器お よ び加算器付 き 2 入力乗算器な ど の数多 く の 3 入力演算機能を構築で き ます。D 入力では、2 つ目の引数を前置加 算器で利用可能に し 、 対称型フ ィ ル タ で使用す る XtremeDSP ス ラ イ ス数を削減 し ます。

アーキテ ク チ ャのハイ ラ イ ト

Spartan-3A DSP ス ラ イ ス は、 縦方向の DSP コ ラ ムで構成 さ れてい ます。DSP コ ラ ム内では、1 つ の DSP ス ラ イ ス が追加の ロ ジ ッ ク お よ び配線に結合 さ れてい ます。Spartan-3A DSP ス ラ イ ス の高 さ は CLB 4 個分です。 各 DSP48A ス ラ イ ス には、 選択可能な 18 ビ ッ ト の前置加算器があ り ます。 こ の前置加算器は、18 ビ ッ ト の 2 の補数入力を受け取 り 、2 の補数の結果を 18 ビ ッ ト で生成 し ます。 前置加算器には、2 入力乗算器、 累算器お よ び 2 入力加算/減算器が後続 し ます。 乗算器は 18 ビ ッ ト の 2 の補数入力 2 本か ら 、36 ビ ッ ト の 2 の補数の結果を出力 し ます。 結果は 48 ビ ッ ト に符号拡張 さ れ、 オプシ ョ ン で加算/減算器に送信で き ます。 加算/減算器は 48 ビ ッ ト の 2 の補数入力 2 本か ら 、48 ビ ッ ト の 2 の補数の結果を 1 つ出力 し ます。 DSP48A コ ラ ム で個々の DSP48A ス ラ イ ス を カ ス ケー ド 接続す る と 、 よ り 高性能な DSP 機能が実 現で き ます。入力 1 つ (B 入力バ ス を カ ス ケー ド) と DSP48A ス ラ イ ス出力 (P 出力バ ス を カ ス ケー ド) でカ ス ケー ド 機能が利用可能です。 た と えば、FIR (有限 イ ンパルス応答) フ ィ ル タ デザ イ ンは、 カ ス ケー ド 入力を使用 し て連続 し たデー タ を入力 し 、 カ ス ケー ド 出力を使用 し て部分的な出力結果 を ま と め ます。 こ の手法の詳細は、34 ページの 「加算器カ ス ケー ド お よ び加算器ツ リ ー」を参照 し て く だ さ い。 DSP48A ス ラ イ スアーキ テ ク チ ャ の特長 • 2 入力前置加算器で対称型フ ィ ル タ を効率的に実現 • 18 x 18 ビ ッ ト の 2 の補数乗算器で 48 ビ ッ ト に符号拡張 し た高精度な 36 ビ ッ ト の結果を出力 • 2 入力で柔軟な 48 ビ ッ ト の後置加算/減算器 (レ ジ ス タ を使用 し た累算フ ィ ー ド バ ッ ク のオプ シ ョ ン付 き) • ク ロ ッ クサ イ ク ルご と に DSP48A ス ラ イ ス の動作モー ド を変更可能 • 18 ビ ッ ト の B バ ス を カ ス ケー ド 接続 し 、 入力デー タ を転送可能 • 48 ビ ッ ト の P バ ス を カ ス ケー ド 接続 し 、 途中結果を転送可能 • コ ン フ ィ ギ ュ レーシ ョ ン ビ ッ ト で選択可能なパ イ プ ラ イ ン オプシ ョ ンに よ っ て制御信号およ びデータ 信号のパフ ォーマン ス を向上可能 • 積和演算、 ビ ッ ト 幅が大き い 2 つのデー タ の加算、 丸め込みモー ド の実現な ど に使用 さ れ る 入 力ポー ト C• 追加の制御レ ジ ス タ と データ レ ジ ス タ に個別の リ セ ッ ト お よ び ク ロ ッ ク イ ネーブル

• 領域を使用せずに最高の ク ロ ッ ク 性能およびサンプルレー ト を実現する I/O レ ジ ス タ

各種の ソ フ ト ウ ェ アツールが DSP48A ス ラ イ ス をサポー ト し てい ます。 ザ イ リ ン ク ス ISE™ ソ フ ト ウ ェ ア ツールは DSP48A ス ラ イ ス の イ ン ス タ ン シエーシ ョ ン を、 ま た、XST な ど の合成ツール

は DSP48A の推論を サポー ト し ま す。CORE Generator™、DSP の System Generator™、 お よ び

AccelDSP™ では、Spartan-3A DSP フ ァ ミ リ を タ ーゲ ッ ト と す る デザ イ ンで DSP48A を使用す る

こ と で、 数値演算、DSP、 さ ら にそれ ら と 類似の Spartan-3A DSP DSP48A ス ラ イ ス を用い る 機能 の生成が容易にな り ます。

Spartan-3A DSP

デバイ ス別の

DSP48A

ス ラ イ ス数

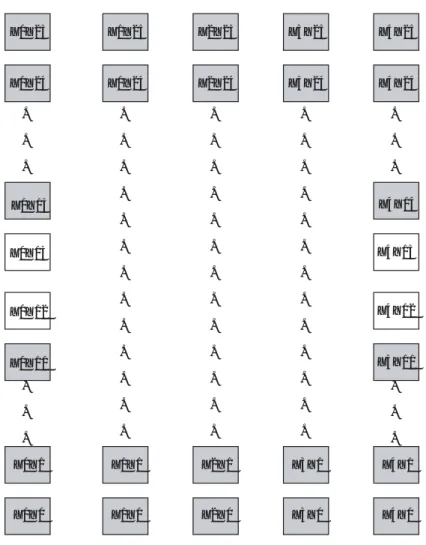

表 1-1に、Spartan-3A DSP フ ァ ミ リ の各デバ イ ス の DSP48A ス ラ イ ス数を示 し ます。Spartan-3A

DSP フ ァ ミ リ は、 ロ ジ ッ ク に対す る DSP48A ス ラ イ ス の比率が高いため、 数値演算を重視 し た ア プ リ ケーシ ョ ンに最適です。図 1-1に、XC3SD1800A FPGA 向けの DSP48A の配置図を、図 1-2

に XC3SD3400A FPGA 向けの DSP48A の配置図を示 し ます。

表 1-1 : 各 フ ァ ミ リ メ ンバの DSP48A ス ラ イ ス数

デバイ ス DSP48A コ ラ ム数

XC3SD1800A

84

4

図 1-1 : XC3SD1800A FPGA の DSP48A の配置図 . . . X0Y25 X0Y24 X1Y25 X1Y24 X2Y25 X2Y24 X3Y25 X3Y24 X4Y25 X4Y24 X0Y1 X0Y0 . . . X0Y13 X0Y12 . . . X1Y1 X1Y0 . . . . . . . . . . . . X2Y1 X2Y0 . . . . . . . . . . . . X3Y1 X3Y0 . . . . . . . . . . . . X4Y1 X4Y0 . . . X4Y13 X4Y12 . . . X0Y11 X4Y11 X0Y14 X4Y14 Notes:

1. Gray positions are populated with DSP48As.

2. Clear positions do not contain DSP48As. DSP48A carry chains are also broken in these positions. There are continuous carry chains from X0Y0 to X0Y11, and then from X0Y14 to X0Y25 and from X4Y0 to X4Y11 and from X4Y14 to X4Y25.

図 1-2 : XC3SD3400A FPGA の DSP48A の配置図

.

.

.

X0Y25

X0Y24

X1Y25

X1Y24

X2Y25

X2Y24

X3Y25

X3Y24

X4Y25

X4Y24

X0Y1

X0Y0

.

.

.

X0Y13

X0Y12

.

.

.

X1Y1

X1Y0

.

.

.

.

.

.

.

.

.

.

.

.

X2Y1

X2Y0

.

.

.

.

.

.

.

.

.

.

.

.

X3Y1

X3Y0

.

.

.

.

.

.

.

.

.

.

.

.

X4Y1

X4Y0

.

.

.

X4Y13

X4Y12

.

.

.

X0Y11

X4Y11

X0Y14

X4Y14

Notes:

1. Gray positions are populated with DSP48As.

2. Clear positions do not contain DSP48As. DSP48A carry chains are also broken

in these positions. There are continuous carry chains from X0Y0 to X0Y11,

and then from X0Y14 to X0Y25 and from X4Y0 to X4Y11 and from X4Y14

to X4Y25.

DSP48A

ス ラ イ スのプ リ ミ テ ィ ブ

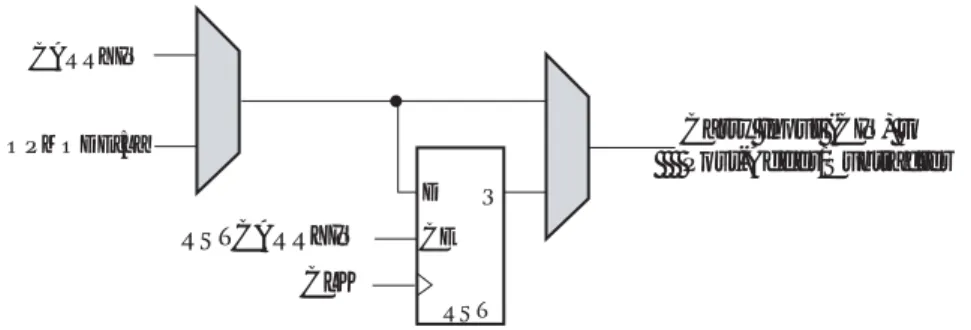

図 1-3に、DSP48A ス ラ イ ス のプ リ ミ テ ィ ブ を示 し ます。 表 1-2に、DSP48A ス ラ イ ス のプ リ ミ テ ィ ブで使用可能なポー ト を示 し ます。 図 1-3 : DSP48A ス ラ イ スのプ リ ミ テ ィ ブ A[17:0] B[17:0] C[47:0] OPMODE[7:0] CARRYIN PCIN[47:0] CLK CEA BCOUT[17:0] P[47:0] PCOUT[47:0] 8 48 18 48 48 CEB CEM CEC CED CECARRYIN RSTA RSTB RSTM RSTC RSTCARRYIN RSTOPMODE CEP RSTP CEOPMODE UG431_c1_01_032007DSP48A

D[17:0] 18 18 48 18 RSTD CARRYOUT 表 1-2 : DSP48A ス ラ イ スポー ト の一覧および説明 信号名 方向 サイ ズ 機能 デー タポー ト A 入力 18 乗算器ま たは後置加算/減算器への 18 ビ ッ ト のデータ 入力 (OPMODE[3:0] の値 に よ る ) B 入力 18 乗算器、 前置加算/減算器、 お よ び場合に よ っ ては後置加算/減算器への 18 ビ ット のデー タ 入力 (OPMODE[4] の値に よ る )。DSP48A UNISIM コ ン ポーネ ン ト が、 隣接す る DSP48A か ら BCOUT を カ ス ケー ド 接続す る 際に こ の入力を 使用す る こ と に留意。 ツールは BCOUT を BCIN 入力に接続 し 、B_INPUT 属 性を イ ンプ リ メ ン テーシ ョ ン用に設定

D 入力 18 前置加算/減算器への 18 ビ ッ ト のデー タ 入力 CARRYIN 入力 1 後置加算/減算器への外部キ ャ リ ー入力。 も う 一方の DSP48A ブ ロ ッ ク の CARRYOUT ピ ンにのみ接続す る 必要があ る P 出力 48 1 番目のデー タ 出力 CARRYOUT 出力 1 後置加算/減算器のキ ャ リ ーア ウ ト 信号。 も う 一方の DSP48A ブ ロ ッ ク の CARRYIN ピ ンにのみ接続す る 必要があ る 制御入力ポー ト CLK 入力 1 DSP48A ク ロ ッ ク

OPMODE 入力 8 DSP48A の演算動作を選択す る 制御入力 (表 1-7の OPMODE 参照)

リ セ ッ ト/ク ロ ッ ク イ ネーブル入力ポー ト RSTA 入力 1 A ポー ト レ ジ ス タ 用のア ク テ ィ ブ High の リ セ ッ ト : A0REG = 1 ま たは A1REG = 1 使用 さ れていない場合は、 ロ ジ ッ ク 0 に固定。 こ の リ セ ッ ト は、RSTTYPE 属 性に よ っ て非同期ま たは同期に設定可能 RSTB 入力 1 B ポー ト レ ジ ス タ 用のア ク テ ィ ブ High の リ セ ッ ト : B0REG = 1 ま たは B1REG = 1 使用 さ れていない場合は、 ロ ジ ッ ク 0 に固定。 こ の リ セ ッ ト は、RSTTYPE 属 性に よ っ て非同期ま たは同期に設定可能 RSTC 入力 1 C 入力レ ジ ス タ (CREG=1) 用のア ク テ ィ ブ High の リ セ ッ ト 。 使用 さ れていな い場合は、 ロ ジ ッ ク 0 に固定。 こ の リ セ ッ ト は、RSTTYPE 属性に よ っ て非同 期ま たは同期に設定可能 RSTD 入力 1 D ポー ト レ ジ ス タ (DREG=1) 用のア ク テ ィ ブ High の リ セ ッ ト 。使用 さ れてい ない場合は、 ロ ジ ッ ク 0 に固定。 こ の リ セ ッ ト は、RSTTYPE 属性に よ っ て非 同期ま たは同期に設定可能 RSTM 入力 1 乗算器レ ジ ス タ (MREG=1) 用のア ク テ ィ ブ High の リ セ ッ ト 。 使用 さ れていな い場合は、 ロ ジ ッ ク 0 に固定。 こ の リ セ ッ ト は、RSTTYPE 属性に よ っ て非同 期ま たは同期に設定可能 RSTP 入力 1 P 出力レ ジ ス タ (PREG=1) 用のア ク テ ィ ブ High の リ セ ッ ト 。 使用 さ れていな い場合は、 ロ ジ ッ ク 0 に固定。 こ の リ セ ッ ト は、RSTTYPE 属性に よ っ て非同 期ま たは同期に設定可能

RSTCARRYIN 入力 1 キ ャ リ ー イ ン レ ジ ス タ (CARRYINREG =1) 用のア ク テ ィ ブ High の リ セ ッ ト 。

使用 さ れていない場合は、 ロ ジ ッ ク 0 に固定。 こ の リ セ ッ ト は RSTTYPE 属性 に よ っ て非同期ま たは同期に設定可能

RSTOPMODE 入力 1 OPMODE レ ジ ス タ (OPMODEREG=1) 用のア ク テ ィ ブ High の リ セ ッ ト 。 使

用 さ れていない場合は、 ロ ジ ッ ク 0 に固定。 こ の リ セ ッ ト は、RSTTYPE 属性 に よ っ て非同期ま たは同期に設定可能 CEA 入力 1 A ポー ト レ ジ ス タ 用のア ク テ ィ ブ High の ク ロ ッ ク イ ネーブル : A0REG = 1、A1REG = 1 使用 さ れていない場合は、 ロ ジ ッ ク 0 に固定。 その後、 次の値に設定。 A0REG = 1、A1REG = 1 A0REG = 0 お よ び A1REG = 0 の場合は ロ ジ ッ ク 0 に固定 表 1-2 : DSP48A ス ラ イ スポー ト の一覧および説明 (続き) 信号名 方向 サイ ズ 機能

CEB 入力 1 B ポー ト レ ジ ス タ 用のア ク テ ィ ブ High の ク ロ ッ ク イ ネーブル :

B0REG = 1 ま たは B1REG = 1

使用 さ れていない場合は、 ロ ジ ッ ク 0 に固定。 その後、 次の値に設定。

B0REG = 1 ま たは B1REG = 1

B0REG = 0 お よ び B1REG = 0 の場合は ロ ジ ッ ク 0 に固定

CEC 入力 1 C ポー ト レ ジ ス タ (CREG=1) 用のア ク テ ィ ブ High の ク ロ ッ ク イ ネーブル。 使

用 さ れていない場合お よ び CREG=1 の と き は、 ロ ジ ッ ク 1 に固定。CREG=0

の場合は、 ロ ジ ッ ク 0 に固定

CED 入力 1 D ポー ト レ ジ ス タ (DREG=1) 用のア ク テ ィ ブ High の ク ロ ッ ク イ ネーブル。使

用 さ れていない場合お よ び DREG=1 の と き は、 ロ ジ ッ ク 1 に固定。DREG=0

の場合は、 ロ ジ ッ ク 0 に固定

CEM 入力 1 乗算器レ ジ ス タ (MREG=1) 用のア ク テ ィ ブ High の ク ロ ッ ク イ ネーブル。 使用

さ れていない場合お よ び MREG=1 の と き は、 ロ ジ ッ ク 1 に固定。MREG=0

の場合は、 ロ ジ ッ ク 0 に固定

CEP 入力 1 出力ポー ト レ ジ ス タ (PREG=1) 用のア ク テ ィ ブ High の ク ロ ッ ク イ ネーブル。

使用 さ れていない場合お よ び PREG=1 の と き は、 ロ ジ ッ ク 1 に固定。

PREG=0 の場合は、 ロ ジ ッ ク 0 に固定

CECARRYIN 入力 1 キ ャ リ ー イ ン レ ジ ス タ (CARRYINREG=1) 用のア ク テ ィ ブ High の ク ロ ッ ク イ

ネーブル。 使用 さ れていない場合お よ び CARRYINREG=1 の と き は、 ロ ジ ッ

ク 1 に固定。CARRYINREG=0 の場合は、 ロ ジ ッ ク 0 に固定

CEOPMODE 入力 1 OPMODE 入力レ ジ ス タ (OPMODEREG=1) 用のア ク テ ィ ブ High の ク ロ ッ ク

イ ネーブル。 使用 さ れていない場合お よ び OPMODEREG=1 の と き は、 ロ ジ ッ ク 1 に固定。OPMODEREG=0 の場合は、 ロ ジ ッ ク 0 に固定 カ スケー ド ポー ト PCIN 入力 48 ポー ト P 用のカ ス ケー ド 入力。 使用 さ れてい る 場合は、 カ ス ケー ド 接続 さ れて い る 上位 DSP48A の PCOUT に接続。 使用 さ れていない場合は、 ポー ト をす べて 0 に固定 BCIN 入力 18 ポー ト B 用のカ ス ケー ド 入力。 使用 さ れてい る 場合は、 カ ス ケー ド 接続 さ れて い る 上位 DSP48A の BCOUT に接続。 使用 さ れていない場合は、 ポー ト をす べて 0 に固定。UNISIM コ ン ポーネ ン ト には、 こ のポー ト がない こ と に留意。 代わ り に、BCOUT を UNISIM コ ン ポーネ ン ト の B ポー ト に接続す る 必要が あ る 。 ツールは BCOUT カ ス ケー ド を BCIN 入力に接続 し 、B_INPUT 属性を イ ンプ リ メ ン テーシ ョ ン用に設定 PCOUT 出力 48 ポー ト P 用のカ ス ケー ド 出力。 使用 さ れてい る 場合は、 カ ス ケー ド 接続 さ れて い る 下位 DSP48A の PCIN に接続。 使用 さ れていない場合は、 未接続の ま ま にす る BCOUT 出力 18 ポー ト B 用のカ ス ケー ド 出力。 使用 さ れてい る 場合は、 カ ス ケー ド 接続 さ れて い る 下位 DSP48A のポー ト B に接続。 使用 さ れていない場合は、 未接続の ま ま にす る 表 1-2 : DSP48A ス ラ イ スポー ト の一覧および説明 (続き) 信号名 方向 サイ ズ 機能

OPMODE

ピ ンの説明

表 1-3に、OPMODE ピ ンの説明を示 し ます。DSP48A

ス ラ イ スの属性

こ の セ ク シ ョ ン では、DSP48A ス ラ イ ス の合成の属性につい て 詳細に説明 し ま す。 B_INPUT、 RSTTYPE、 お よ び CARRYINSEL 属性を除 く すべての属性は、 制御パスお よ びデー タ パ ス上にパ イ プ ラ イ ン レ ジ ス タ を挿入 し ます。 属性値はパ イ プ ラ イ ン レ ジ ス タ の段数を示 し ます。 次に属性の設定を示 し ます。• A0REG、A1REG、B0REG、 お よ び B1REG 属性は、0 ま たは A お よ び B 入力パ ス のパ イ プ

ラ イ ン レ ジ ス タ 数を決定す る 値に設定可能です。 デフ ォ ル ト 値は A0REG では 0 (レ ジ ス タ な

し)、A1REG では 1 (レ ジ ス タ 付 き)、B0REG では 0 (レ ジ ス タ な し)、B1REG では 1 (レ ジ ス

タ 付 き) です。 詳細は、「A、B、C、D、 お よ び P ポー ト ロ ジ ッ ク 」のセ ク シ ョ ン を参照 し て く だ さ い。

• CREG、DREG、MREG、 お よ び PREG 属性は 0 ま たは 1 に設定可能です。 こ の値は、 乗算

器の出力 (MREG、図 1-12参照) お よ び後置加算/減算器の出力 (PREG、図 1-10参照) でパ イ

プ ラ イ ン レ ジ ス タ 数を決定 し ます。GREG 属性は、C 入力でパ イ プ ラ イ ン レ ジ ス タ 数の選択 に使用 さ れます (図 1-9参照)。CREG、DREG、MREG、 お よ び PREG 属性のデフ ォ ル ト はす べて 1 です (レ ジ ス タ 付 き)。 表 1-3 : OPMODE ピ ンの説明 ポー ト 名 機能 OPMODE[1:0] 後置加算/減算器への X 入力の ソ ース を決定 0 – すべてに 0 を配置 (後置加算/減算器を無効にす る) 1 – 乗算器の積を使用 2 – P 出力信号を使用 (累算器) 3 – 連結 し た D、B、A 入力信号を使用 OPMODE[3:2] 後置加算器への Z 入力のソ ース を決定 0 – すべてに 0 を配置 (後置加算/減算器を無効に し 、P への上算器の積を伝搬) 1 – PCIN を使用 2 – P ポー ト を使用 (累算器) 3 – C ポー ト を使用 OPMODE[4] 前置加算/減算器を使用するかを決定 0 – ポー ト B を介 し て直接乗算器へデー タ を送信す る 前置加算器をバ イ パ ス 1 – 乗算器よ り 前に B およ び D ポー ト で値を加算ま たは減算する 前置加算器の使用を選択

OPMODE[5] キ ャ リ ー イ ンの値を後置加算器へ送信。CARRYINSEL = OPMODE5 の場合のみ適用

OPMODE[6] 前置加算/減算器が加算器か減算器かを決定 0 – 前置加算/減算器が加算動作す る 1 – 前置加算/減算器が減算動作す る OPMODE[7] 後置加算器が加算器か減算器かを決定 0 – 後置加算/減算器が加算動作す る 1 – 後置加算/減算器が減算動作す る

• CARRYINREG お よ び OPMODEREG 属性は、 こ れ ら のパス にパ イ プ ラ イ ン レ ジ ス タ がない 場合は 0 に、1 つあ る 場合は 1 に設定 し ます。図 1-11に CARRYINSEL お よ び OPMODEREG

パ ス を、図 1-13に CARRYINREG パ ス を示 し ま す。CARRYINREG お よ び OPMODEREG

のデフ ォ ル ト 値は 1 です (レ ジ ス タ 付 き)。

• CARRYINSEL 属性は、 後置加算/減算器のキ ャ リ ー入力信号が CARRYIN ピ ン (も う 一方の

DSP48A の CARRYOUT 出力に接続) か ら 入力 さ れ る か、OPMODE[5] 入力に よ っ て FPGA

フ ァ ブ リ ッ ク か ら 動的に制御 さ れ る か を決定 し ま す。 こ の属性は、 文字列 CARRYIN ま たは

OPMODE5 に設定可能です。CARRYINSEL はデフ ォ ル ト で CARRYIN です。

• B_INPUT 属性は、B ポー ト への入力の配線が、 パ ラ レル入力 (属性 : DIREDCT)、 ま たは前の ス ラ イ ス か ら カ ス ケー ド 接続 さ れた入力 (属性 : CASCADE)の ど ち ら か ら 配線 さ れ る か を決定 し ます。 こ の属性は配置配線ツールのみで使用 さ れ、 合成では設定す る 必要はあ り ません。 こ の属性は、DSP48A の B ポー ト への接続で決定 さ れます。B ポー ト が も う 一方の DSP48A の BCOUT に接続 さ れ る 場合は、 ツールが属性を自動的に CASCADE に設定 し ます。 そ う でな い場合は、DIRECT に設定 さ れます。 • RSTTYPE 属性は、DSP48A の リ セ ッ ト すべてに同期ま たは非同期の リ セ ッ ト 機能を付け る か ど う か を決定 し ます。 こ の属性は、ASYNC ま たは SYNC に設定可能です。 タ イ ミ ン グの向上 お よ び回路の安定性の た め、 非同期 リ セ ッ ト が絶対に必要で な い限 り は、 こ の属性 を 常に

SYNC に設定す る こ と を推奨 し ます。RSTTYPE はデフ ォ ル ト で SYNC です。

VHDL

および

Verilog

のイ ン ス タ ン シ エーシ ョ ン

テ ン プ レー ト

DSP48A ス ラ イ ス用の VHDL お よ び Verilog での イ ン ス タ ン シエーシ ョ ン テ ン プ レー ト は、ISE

ツールの次の メ ニ ュ ーか ら 入手可能です。

ISE → [Edit] → [Language Templates] → [VHDL || Verilog] → [Device Primtive Instantiation] → [Arithmetic Functions] → [Spartan-3A DSP] → [DSP BLock (DSP48A)]

DSP48A

ス ラ イ スおよび イ ン タ ー コ ネ ク ト

DSP48A ス ラ イ ス は、DSP48A コ ラ ム に縦方向に積み重な っ てい ます (表 1-1参照)。DSP48A ス

ラ イ ス の高 さ は、CLB 4 個分ま たはブ ロ ッ ク RAM 1個分の高 さ と 同等です。 こ の 「規則性」 に よ っ

て 幅 の広いデー タ パ ス の配線効率が向上 し ま す。DSP48A コ ラ ム は、 小型の Spartan-3A DSP

(XC3SD1800A) フ ァ ミ リ には 4 つ、 大型の Spartan-3A DSP (XC3SD3400A) フ ァ ミ リ には 5 つあ

り ます。

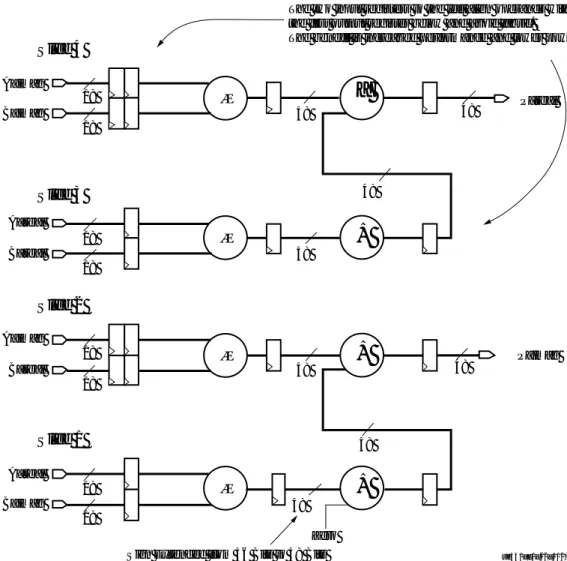

乗算器お よ びブ ロ ッ ク RAM は、Virtex-II お よ び Virtex-II Pro アーキ テ ク チ ャ では イ ン タ ー コ ネ ク ト リ ソ ース を共有 し てい ます。Spartan-3A DSP デバ イ ス には DSP48A ス ラ イ スお よ びブ ロ ッ ク RAM 用の独立 し た配線があ る ため、エ レ メ ン ト 間の利用可能なデー タバン ド 幅が 2 倍にな り ます。 図 1-4に、DSP48A の イ ン タ ー コ ネ ク ト と 関連す る 専用エ レ メ ン ト のサ イ ズ を示 し ます。 図 1-5に、 DSP48A コ ラ ム に縦方向に積み重な る DSP48A ス ラ イ スお よ びそれに関連す る デー タ パス を示 し ます。 灰色で表示 さ れたマルチプ レ ク サへの入力は、 コ ン フ ィ ギ ュ レーシ ョ ン制御信号 で選択 さ れます。 こ れ ら の属性は、HDL ソ ース コ ー ド ま たは UCF (ユーザー制約フ ァ イ ル) で設定 さ れます。 図 1-4 : DSP48A の配置 CLB CLB CLB CLB CLB CLB CLB CLB DS P 48A DS P 48A CLB CLB CLB CLB CLB CLB CLB CLB CLB CLB CLB CLB CLB CLB CLB CLB CLB CLB CLB CLB CLB CLB CLB CLB CLB CLB CLB CLB CLB CLB CLB CLB CLB CLB CLB CLB CLB CLB CLB CLB Block RAM Block RAM ug431_ch1_03_030807

メ モ : 1. 18 ビ ッ ト の A、B、 お よ び D バ ス は、D[11:0]、A[17:0]、B[17:0] の順番で連結 さ れてい ます。 2. X お よ び Z マルチプ レ ク サは 48 ビ ッ ト で設計 さ れてい ます。36 ビ ッ ト 入力を選択す る と 、48 ビ ッ ト の符 号拡張出力が生成 さ れます。 3. マルチプ レ ク サは、36 ビ ッ ト の結果を出力 し ます。 4. P の乗算累算器パス は、Z マルチプ レ ク サを介 し ます。X マルチプ レ ク サを通 る P フ ィ ー ド バ ッ ク は、 乗 算器が使用 さ れていない場合に P カ ス ケー ド の合計値を出力 し ます。 5. 灰色で表示 し たマルチプ レ ク サは、 コ ン フ ィ ギ ュ レーシ ョ ン時にプ ロ グ ラ ム さ れます。 6. C レ ジ ス タ は乗算-加算、 ま たは値が大 き い加算をサポー ト し ます。C レ ジ ス タ は、DSP48A ブ ロ ッ ク の専 用レ ジ ス タ です。 こ れは、1 つの C レ ジ ス タ が 2 つの DSP48 ブ ロ ッ ク で共有 さ れていた Virtex DSP48 ブ ロ ッ ク の C レ ジ ス タ と は異な り ます。 7. SUBTRACT を有効にす る と 、 後置加算/減算器の出力時が Z – (X + CARRYIN) と な り ます。 8. B 入力は、 前置加算/減算器を使用 し て D 入力 と 加算ま たは減算可能です。 9. 前置加算器の入力 (B と D) お よ び出力は 18 ビ ッ ト 幅です。18 ビ ッ ト 入力が 2 つあ る と オーバーフ ロ ーが 発生す る ため、 こ の点を考慮す る 必要があ り ます。 図 1-5 : DSP48A ス ラ イ ス B 18 UG431_c1_03_032207 D 18 A 18 C 48 18 BCIN D REG B0 REG A0 REG C REG

+

18 +/- B1 REG A1 REG×

M REG opmode[6] opmode[4]+

X Z P REG opmode[5] CARRYIN +/- opmode[7] opmode[3:2] opmode[1:0] PCIN 0 0 48 48 48 48 36 48 Pre-AdderBCOUT PCOUT CARRYOUT

Post-Adder/ Subtracter Carry Cascade P D:A:B Concatenated Pre-Adder Dedicated C-Port 18 18 48 48

DSP48E

ス ラ イ ス動作の概略

DSP48A ス ラ イ ス の演算部分には、18 ビ ッ ト の前置加算器があ り 、 その後に 18 x 18 ビ ッ ト の 2 の 補数乗算器があ り ます。 さ ら に 48 ビ ッ ト デー タ パ ス のマルチプ レ ク サ (X お よ び Z 出力付 き) が 2 つあ り 、 その後に 2 入力 48 ビ ッ ト の後置加算/減算器があ り ます。 DSP48A ス ラ イ ス のデー タ 入力お よ び制御入力は、 演算回路で直接接続す る か、 あ る いはオプシ ョ ン で 1 つま たは 2 つの レ ジ ス タ を挿入で き る ため、 パ イ プ ラ イ ン段数の異な る DSP 処理を実現で き ます。A ま たは B のデー タ 入力は、 オプシ ョ ンで 1 段ま たは 2 段の レ ジ ス タ を使用で き ます。 そ の他のデー タ 入力お よ び制御入力は、 オプシ ョ ン と し て 1 段の レ ジ ス タ を使用で き ます。 パ イ プ ラ イ ンレ ジ ス タ を使用 し た場合、 最高速度は 250MHz と な り ます。論理式

基本的に、 後置加算/減算器の出力は、 その入力のフ ァ ン ク シ ョ ンです。 入力は上位マルチプ レ ク サ、 キ ャ リ ーセ レ ク ト ロ ジ ッ ク 、 およ び乗算ア レ イ で駆動 さ れます。数式1-1に、 後置加算/減算器に よ る X、Z、 およ び CARRYIN の組み合わせを示し ます。CARRYIN およ び X マルチプ レ ク サの出力 は常に加算 さ れます。 こ の結果を、Z マルチプ レ ク サ出力に対し て加算ま たは減算で き ます。 加算出力= (Z ± (X + CARRYIN)) 数式1-1

数式1-2は、A お よ び B 入力が乗算 さ れ、 結果が C レ ジ ス タ へ加算ま たは減算 さ れ る 典型的な使 用例を示 し てい ます。 制御入力お よ びデー タ 入力に関す る 詳細は、 こ のセ ク シ ョ ンの後半で説明 し ます。 乗算器フ ァ ン ク シ ョ ン を選択す る と 、X マルチプ レ ク サ出力を使用 し て加算器へ送信 さ れま す。 乗算器か ら 出力 さ れた 36 ビ ッ ト の積は、 後置加算/減算器に送信 さ れ る 前に 48 ビ ッ ト へ符号 拡張 さ れます。 加算出力= C ± (A x B + CARRYIN) 数式1-2

数式1-3では、B お よ び D が、 最初は前置加算/減算器を使用 し て加算 さ れ、 前置加算の結果が A に対 し て乗算 さ れます。 その乗算結果が C 入力に加算 さ れます。 こ れに よ り 対称型フ ィ ル タ を効率 的に実現で き ます。 出力加算= C ± (A x (D ± B) + CARRYIN) 数式1-3

図 1-6に、DSP48A ス ラ イ ス の簡略図を示 し ます。8 ビ ッ ト の OPMODE が、 マルチプ レ ク サの 48 ビ ッ ト デー タパ ス の選択を制御 し 、 後置加算/減算器のそれぞれ 2 つの入力お よ び乗算器の B 入力 へ接続 し ま す。 ま た、OPMODE ビ ッ ト は前置加算/減算器 ま たは後置加算/減算器の加算 ま たは減 算を制御 し ます。 いずれの場合で も 、乗算器へ渡 さ れ る 36 ビ ッ ト の入力デー タ は符号拡張 さ れ、48 ビ ッ ト デー タ と し て後置加算/減算器への入力 と な り ます。36 ビ ッ ト の入力デー タ と 48 ビ ッ ト の後 置加算器出力ビ ッ ト の差が、 「ガー ド ビ ッ ト 」 (オーバーフ ロ ーか ら 保護す る ビ ッ ト) の 12 ビ ッ ト と な り ま す。 し た が っ て、 オ ー バ ー フ ロ ー が 発 生 す る ま で に 可 能 な 乗 算 累 算 数 は 4096 で す。OPMODE、CARRYINSEL、 お よ び CARRYIN の組み合わせで前置お よ び後置加算/減算器の フ ァ

A

、

B

、

C

、

D

、 および

P

ポー ト

ロ ジ ッ ク

DSP48A 入力お よ び出力デー タ ポー ト は、 多 く の一般的な DSP お よ び数値演算アルゴ リ ズ ムに対 応 し てい ます。DSP48A ス ラ イ ス には、18 ビ ッ ト の直接入力デー タ ポー ト が 3 つ (A、B、D) と 、 48 ビ ッ ト の入力データ ポー ト (C) が 1 つあ り ます。 各 DSP48A ス ラ イ ス には、48 ビ ッ ト の直接出 力ポー ト (P) があ り ます。 ま た、DSP48A ス ラ イ ス には、 カ ス ケー ド 接続 さ れた入力デー タパ ス (B カ ス ケー ド) およ び出力データパス (P カ ス ケー ド) があ り 、隣接する DSP48A ス ラ イ ス と の入力 およ び出力を カ ス ケー ド 接続 し ます。B カ ス ケー ド は、 隣接の DSP48A ス ラ イ ス に接続 し てい る 専 用の リ ソ ース で、B_INPUT 属性で使用お よ び不使用が設定 さ れ ま す。 ま た、DSP48A ス ラ イ ス には、CARRYIN 入力およ び CARRYOUT 出力が存在 し ます。こ れ ら の リ ソ ースは、隣接する DSP48A

ス ラ イ ス の並列 MACC 回路の作成に使用 さ れます。PCIN カ ス ケー ド は、隣接の DSP48A ス ラ イ ス

に常に接続 さ れてい る 専用 リ ソ ース で、Z MUX (OPMODE 3:2) で動的に選択可能です。 こ れ ら の機能は、FIR フ ィ ル タ 、 複素乗算、 高精度乗算、 複素 MAC、 加算器カ ス ケー ド 、 加算器ツ リ ー (複数の乗算器か ら の出力をすべて加算) を用い る アプ リ ケーシ ョ ンに有効です。 18 ビ ッ ト の D お よ び B 入力は、18 ビ ッ ト の前置加算/減算器に入力デー タ を供給で き ます。 前置 加算/減算器は、 設定に よ っ てバ イ パス可能です。 前置加算器の出力は、 必要であれば OPMODE[4] を使用 し て乗算器の入力の 1 つに接続可能です。 18 ビ ッ ト の A お よ び B ポー ト は、18 x 18 ビ ッ ト の 2 の補数乗算器に入力デー タ を供給で き ます。 D、A お よ び B は連結 さ せ る と 乗算器をバ イ パ ス で き 、X マルチプ レ ク サ入力に直接接続可能です。 48 ビ ッ ト の C ポー ト は、 加算ま たは減算のための Z マルチプ レ ク サへの汎用入力 と し て使用 さ れ ます。 コ ン フ ィ ギ ュ レーシ ョ ンビ ッ ト で制御 さ れ る マルチプ レ ク サは、 直接接続パ ス、 オプシ ョ ンの レ ジ ス タ 、 ま たはカ ス ケー ド 入力を選択 し ます。 デー タ ポー ト レ ジ ス タ に よ っ て ク ロ ッ ク 周波数の上 昇 (パ フ ォ ーマ ン ス 向上) が可能にな り ま すが、 デー タ レ イ テ ン シ と の ト レー ド オ フ が生 じ ま す。 ま た、 乗算器お よ び加算/減算器間の コ ン フ ィ ギ ュ レーシ ョ ン で制御 さ れ る パ イ プ ラ イ ン レ ジ ス タ は、M レ ジ ス タ と し て知 ら れてい ます。 こ の レ ジ ス タ には、表 1-2お よ び図 1-3に示す独立 し た ク ロ ッ ク イ ネーブルお よ び リ セ ッ ト があ り ます。 図 1-6 : DSP48A ス ラ イ スの簡略図 CARRYIN CARRYOUT P Z Zero P PCIN C OPMODE, CARRYIN Controls Behavior ug431_ch1_04_012307 P X D B A OPMODE Controls Behavior D:A:B concat Zero

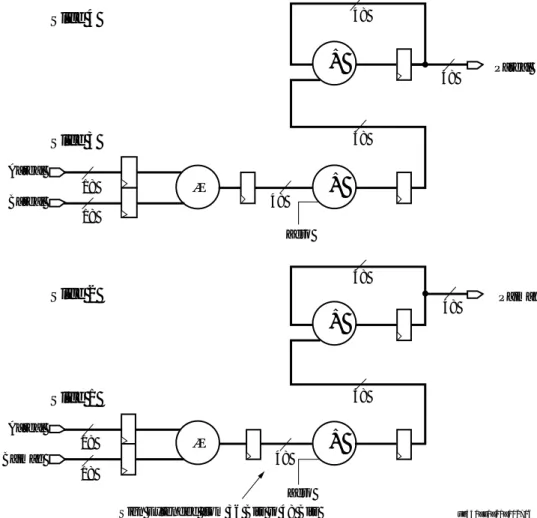

A、B、C、お よ び P ポー ト ロ ジ ッ ク を それぞれ図 1-7、図 1-8、図 1-9、お よ び図 1-10に示 し ます。 図 1-7 : A 入力ロ ジ ッ ク RST EN D Q A 18 18 18 18 RST EN D Q RSTA CEA A Input to Multiplier ug431_c1_06_020207 0 1 0 1 CLK CLK A0 REG A1 REG 図 1-8 : B お よび D 入力ロ ジ ッ ク B Input to Multiplier RST EN D Q 18 B 18 18 18 18 RST EN D Q RSTB CEB BCIN ug431_c1_07_103007

±

18 RST EN D Q CED RSTD D 18 OPMODE[4] Pre-adder/subtracter D REG B1 REG B0 REGメ モ : 灰色で表示 し たマルチプ レ ク サは、 コ ン フ ィ ギ ュ レーシ ョ ン時にプ ロ グ ラ ム さ れます。 無色で表示 し たマルチプ レ ク サは、 動的に変更可能で OPMODE ビ ッ ト を使用 し て変更で き ます。

OPMODE

ポー ト

ロ ジ ッ ク

OPMODE ポー ト ロ ジ ッ ク は、OPMODE 信号への レ ジ ス タ 挿入お よ び非挿入を選択 し ます。 デー タパ ス と 同様、 コ ン フ ィ ギ ュ レーシ ョ ン ビ ッ ト で制御 さ れ る マルチプ レ ク サが、 オプシ ョ ン の レ ジ ス タ の使用を選択 し ます。 制御ポー ト レ ジ ス タ に よ っ て ク ロ ッ ク 周波数を上昇 (パフ ォーマ ン ス を向上) さ せ る こ と が可能にな り ますが、 デー タ レ イ テ ン シ と の ト レー ド オ フ が生 じ ます。 レ ジ ス タ には独立 し た ク ロ ッ ク イ ネーブル と リ セ ッ ト 信号があ り ます (表 1-2お よ び図 1-3参照)。OPMODE レ ジ ス タ は RSTO で リ セ ッ ト さ れ ます。OPMODE レ ジ ス タ には、CEO と 表示 さ れた

イ ネーブルが別にあ り ます。図 1-11に、OPMODE ポー ト ロ ジ ッ ク を示 し ます。 図 1-9 : C 入力ロ ジ ッ ク 図 1-10 : P 出力ロ ジ ッ ク RST EN D Q

CLK

48 48 48RSTC

CEC

C

To Z Multiplexer

ug431_c1_08_020207C REG

RST EN D Q 48 48 48RSTP

CEP

P

DSP48A

Slice Output

ug431_c1_09_020207From Post-Adder/

Subtracter Output

P REG

図 1-11 : OPMODE ポー ト ロ ジ ッ クTo the X and Z Multiplexers control for pre- and post-adder/subtracters and Carry Input Select Logic

RST EN D Q 8 OPMODE CEO RSTO 8 ug431_c1_10_011007

2

の補数乗算器

DSP48A ス ラ イ ス内の 2 の補数乗算器は、18 ビ ッ ト の 2 の補数入力 2 本か ら 、36 ビ ッ ト の 2 の補 数結果を 1 つ出力 し ます。よ り 大 き な ビ ッ ト 幅の積を得 る ために乗算器を カ ス ケー ド 接続す る には、 フ ァ ブ リ ッ ク に イ ン プ リ メ ン ト 済みの 17 ビ ッ ト 右シ フ ト し たバ ス を使用 し ます。 こ のバ ス は、 後 置加算/減算器への入力に接続 し 、 右シ フ ト を使用 し て、 適切な ビ ッ ト 数だけ部分積を右揃えに し ま す。 ま た、MACC 機能は、 結果の精度を高め る ために中間積を右揃えにで き ます。18 ビ ッ ト のオ ペ ラ ン ド の MSB (最上位ビ ッ ト) を 0 に設定す る と 、 乗算器は符号な し の演算を行え ます。 乗算器の出力は、36 ビ ッ ト の積で構成 さ れてい ます。 積は、 加算/減算器に入力 さ れ る 前に 48 ビ ッ ト に符号拡張 さ れます。 乗算器出力を選択す る 場合、X マルチプ レ ク サが使用 さ れます。 図 1-12に、 乗算器出力用のオプシ ョ ンのパ イ プ ラ イ ン レ ジ ス タ (MREG) を示 し ます。 レ ジ ス タ を 使用す る と 、1 ク ロ ッ ク レ イ テ ン シが付 き ますがパフ ォーマ ン ス は向上 し ます。 灰色で表示 し たマ ルチプ レ ク サは、 コ ン フ ィ ギ ュ レーシ ョ ン時に コ ン フ ィ ギ ュ レーシ ョ ン ビ ッ ト に よ っ て選択 さ れて い ます。X

お よび

Z

マルチ プ レ クサ

OPMODE 入力は、 ク ロ ッ ク ご と に機能を変更で き ます (た と えば、 与え ら れた計算の中間部分に 対 し て、DSP48A の初期ま たは最終ス テー ト を変更す る 場合な ど)。OPMODE ビ ッ ト は、 コ ン フ ィ ギ ュ レーシ ョ ン メ モ リ セルの制御に よ っ てオプシ ョ ンの レ ジ ス タ を設定で き ます (図 1-11の灰色 表示 し たマルチプ レ ク サに関す る メ モ参照)。 表 1-4お よ び表 1-5に、OPMODE で使用可能な値お よ び 2 つのマルチプ レ ク サ (X お よ び Y マル チプ レ ク サ) の出力結果を示 し ます。 マルチプ レ ク サは、 後続の加算/減算器への 3 つのデー タ を出 力 し ます。 乗算出力が選択 さ れてい る 場合は、X マルチプ レ ク サを使用 し てマルチプ レ ク サの出力 が後置加算/減算器へ送信 さ れます。 表 1-6に、OPMODE[7:4] お よ びその機能を示 し ます。 図 1-12 : 2 の補数乗算器 と オプ シ ョ ンの MREG 36A

Optional

MREG

ug431_c1_11_011007×

±

B

D

To X mux input 36次に、2 つのマルチプ レ ク サに よ っ て選択 さ れた後置加算/減算器の 0 以外のオペ ラ ン ド を示 し ます。 • 乗算器出力 (36 ビ ッ ト) • B お よ び D と 連結 し た A に よ る 乗算器バ イ パス バ ス • C バ ス (48 ビ ッ ト) • 隣接する DSP48A ス ラ イ ス か ら カ ス ケー ド 接続 さ れた P バ ス (48 ビ ッ ト) • 累算機能用のレ ジ ス タ付き P バ ス出力 (48 ビ ッ ト) • 累算機能用のレ ジ ス タ付き P バ ス出力 メ モ : 36 ビ ッ ト のオペ ラ ン ド はすべて 48 ビ ッ ト に符号拡張済みです。 表 1-4 : OPMODE 制御ビ ッ ト および X マルチ プ レ クサ出力 バイ ナ リ の OPMODE 後置加算/減算器に送信 さ れる X マルチ プ レ ク サ出力 Z OPMODE[3:2] X OPMODE[1:0] XX 00 0 (デフ ォ ル ト) XX 01 マルチプ レ ク サ出力 XX 10 P XX 11 B[17:0] に結合 し た A[17:0] に連結す る D[11:0] 表 1-5 : OPMODE 制御ビ ッ ト および Z マルチ プ レ クサ出力 バイ ナ リ の OPMODE 後置加算/減算器に送信 さ れる Z マルチ プ レ クサ出力 Z OPMODE[3:2] X OPMODE[1:0] 00 XX 0 (デフ ォ ル ト) 01 XX PCIN 10 XX P 11 XX C 表 1-6 : OPMODE[7:4] の機能の説明 OPMODE 機能の説明 OPMODE[7] 後置加算/減算器。1 = 減算 OPMODE[6] 前置加算/減算器。1 = 減算 OPMODE[5] ユーザー CARRYIN ビ ッ ト OPMODE[4] B 入力 1 = 前置加算/減算器を使用

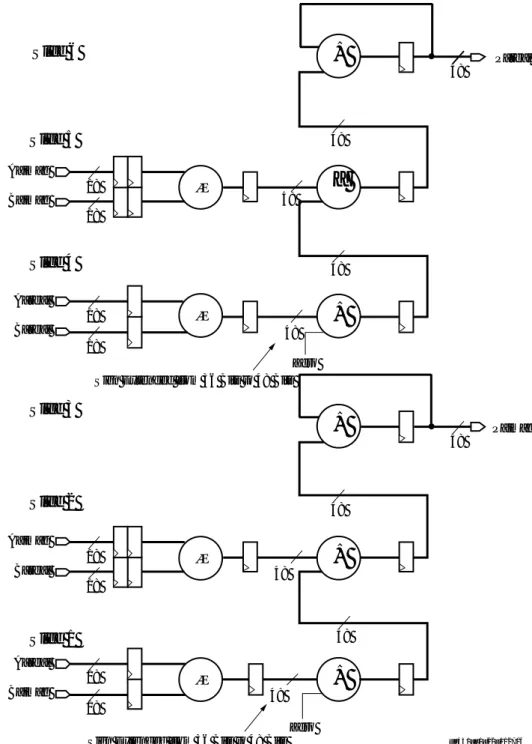

表 1-7に、 すべてのDSP48A 動作モー ド を示 し ます。 表 1-7 : DSP48A 動作モー ド OPMODE OPMODE[7:0] CARR YINSEL 出力 後置加算 / 減算器 前置加算 / 減算器 CARR YIN 前置加算 / 減算器 セレ ク ト Z X 7 6 5 4 3 2 1 0 0 + CARRYIN 0 0/1 0/1 0/1 0 0 0 0 0 + CARRYIN 0 – CARRYIN 1 0/1 0/1 0/1 0 0 0 0 0 – CARRYIN 0 + OPMODE<5> 0 0/1 0/1 0/1 0 0 0 0 1 + OPMODE[5] 0 – OPMODE<5> 1 0/1 0/1 0/1 0 0 0 0 1 – OPMODE[5] P を ホール ド 0/1 0/1 0/1 0/1 0 0 1 0 0/1

±

(P + CARRYIN)D:A:B セ レ ク ト 0/1 0/1 0/1 0 0 0 1 1 0/1

±

(D:A:B + CARRYIN)D:A:B セ レ ク ト (前置加算付 き) 0/1 0/1 0/1 1 0 0 1 1 0/1

±

(D:A:(D±

B) + CARRYIN)乗算 0/1 0/1 0/1 0 0 0 0 1 0/1

±

(A×

B + CARRYIN)前置加算-乗算 0/1 0 0/1 1 0 0 0 1 0/1

±

(A×

(D + B) + CARRYIN)前置減算-乗算 0/1 1 0/1 1 0 0 0 1 0/1

±

(A×

(D – B) + CARRYIN)P カ ス ケー ド セ レ ク ト 0/1 0/1 0/1 0/1 0 1 0 0 0/1 PCIN

±

CINP カ ス ケー ド フ ィ ー ド バ ッ ク 加算 0/1 0/1 0/1 0/1 0 1 1 0 0/1 PCIN

±

(P + CARRYIN)P カ ス ケー ド 加算 0/1 0/1 0/1 0 0 1 1 1 0/1 PCIN

±

(D:A:B + CARRYIN)P カ ス ケー ド 加算 (前置加算付 き) 0/1 0/1 0/1 1 0 1 1 1 0/1 PCIN

±

(D:A:(D±

B) + CARRYIN P カ ス ケー ド 乗算加算 0/1 0/1 0/1 0 0 1 0 1 0/1 PCIN±

(A×

B + CARRYIN) カ ス ケー ド 前置加算-乗算 0/1 0 0/1 1 0 1 0 1 0/1 PCIN±

(A×

(D + B) + CARRYIN) カ ス ケー ド 前置減算-乗算 0/1 1 0/1 1 0 1 0 1 0/1 PCIN±

(A×

(D – B) + CARRYIN) フ ィ ー ド バ ッ クキ ャ リ ー入力加算 0/1 0/1 0/1 0/1 1 0 0 0 0/1 P ± CARRYIN 二重フ ィ ー ド バ ッ ク 加算 0/1 0/1 0/1 0/1 1 0 1 0 0/1 P±

(P + CARRYIN) フ ィ ー ド バ ッ ク 加算 0/1 0/1 0/1 0 1 0 1 1 0/1 P±

(D:A:B + CARRYIN) フ ィ ード バッ ク 加算 (前置加算付き) 0/1 0/1 0/1 1 1 0 1 1 0/1 P±

(D:A:(D ± B) + CARRYIN) 乗算-累算 0/1 0/1 0/1 0 1 0 0 1 0/1 P±

(A×

B + CARRYIN) フ ィ ー ド バ ッ ク 前置加算-乗算 0/1 0 0/1 1 1 0 0 1 0/1 P ± (A×

(D + B) + CARRYIN) フ ィ ー ド バ ッ ク 前置減算-乗算 0/1 1 0/1 1 1 0 0 1 0/1 P ± (A×

(D – B) + CARRYIN) C セ レ ク ト 0/1 0/1 0/1 0/1 1 1 0 0 0/1 C ± CARRYIN フ ィ ー ド バ ッ ク 加算 0/1 0/1 0/1 0/1 1 1 1 0 0/1 C ± (P + CARRYIN) 48 ビ ッ ト 加算 0/1 0/1 0/1 0 1 1 1 1 0/1 C ± (D:A:B + CARRYIN) 乗算-加算 0/1 0/1 0/1 0 1 1 0 1 0/1 C ± (A×

B + CARRYIN) C 前置加算-乗算 0/1 0 0/1 1 1 1 0 1 0/1 C ± (A×

(D + B) + CARRYIN) C 前置減算-乗算 0/1 1 0/1 1 1 1 0 1 0/1 C ± (A×

(D – B) + CARRYIN)前置加算

/

減算器

前置加算/減算器の出力は、OPMODE[6] と B お よ び D デー タ 入力の フ ァ ン ク シ ョ ンです。 前置加 算器は、 対称型 フ ィ ル タ の リ ソ ー ス 使用率 を 削減 し ま す。 OPMODE[6] は、 信号 を 制御 し ま す (OPMODE[6] = 1 を減算 と 定義)。 ま た、3 入力の加算器用に後置加算器を組み合わせ る こ と も 可能 です。後置加算器

/

減算器

/

累算器

後置加算器/減算器/累算器出力は OPMODE お よ びデー タ 入力の フ ァ ン ク シ ョ ン です。 前のセ ク シ ョ ンで示す よ う に、OPMODE[3:0] は後置加算/減算器の入力に接続す る X ま たは Z マルチプ レ ク サへの入力値を選択 し ます。 表 1-4お よ び表 1-5に、OPMODE の組み合わせお よ び結果の フ ァ ン ク シ ョ ン を示 し ます。 表内の ± は、 加算ま たは減算を示 し 、OPMODE[7] 制御信号 (OPMODE[7] = 1 を減算 と 定義) の ス テー ト に よ っ て決定 さ れます。X マルチプ レ ク サお よ び CARRYIN (CARRYSELECT ビ ッ ト のプ ロ グ ラ ミ ン グに よ っ ては OPMODE[5]) の出力は常に合算 さ れます。 その後、 こ の結果は Z マルチプ レ ク サの出力に対 し て加算ま たは減算 さ れます。キ ャ リ ー入力ロ ジ ッ ク

キ ャ リ ー 入 力 ロ ジ ッ ク の 結 果 は、CARRYIN セ レ ク ト コ ン フ ィ ギ ュ レ ー シ ョ ン ビ ッ ト 、 OPMODE[5]、 お よ び CARRYIN の フ ァ ン ク シ ョ ンです。図 1-13に、 キ ャ リ ー入力 ロ ジ ッ ク の入 力を示 し ます。 加算器お よ び減算器用の結果を生成す る キ ャ リ ー入力は、 常に ク リ テ ィ カルパ ス上 にあ り ます。 こ の ロ ジ ッ ク を拡散シ リ コ ン上に イ ンプ リ メ ン ト す る こ と で、 高パフ ォーマ ン ス が実 現 し ます。 キ ャ リ ー ロ ジ ッ ク が可能な キ ャ リ ー入力は、X お よ び Z マルチプ レ ク サの出力の前に 配置 さ れ ます。 し たが っ て、X お よ び Z マルチプ レ ク サの フ ァ ン ク シ ョ ンは、 キ ャ リ ー ロ ジ ッ ク への キ ャ リ ー入力用に重複 し ま す。OPMODE お よ び CARRYINSEL は、 正 し い キ ャ リ ー入力 (CARRYIN) を確実に選択す る よ う 、 正 し い ス テー ト と な っ てい る 必要があ り ます。 48 ビ ッ ト 加算 (前置加算付 き) 0/1 0/1 0/1 1 1 1 1 1 0/1 C ± (D:A:(D ± B) + CARRYIN) メ モ :1. 残 り の機能では CARRYIN = CARRYIN 出力は、 こ のセ ク シ ョ ンに示す CARRY SEL のプ ロ グ ラ ミ ン グに よ っ て上位 DSP48A ブ ロ ッ ク ま たは OPMODE[5] か ら 送信 さ れます。 2. 出力マルチプ レ ク サは、 レ ジ ス タ 出力を選択す る 必要があ り ます。 3. 1 の場合はすべて加算 さ れます。 表 1-7 : DSP48A 動作モー ド (続き) OPMODE OPMODE[7:0] CARR YINSEL 出力 後置加算 / 減算器 前置加算 / 減算器 CARR YIN 前置加算 / 減算器 セレ ク ト Z X 7 6 5 4 3 2 1 0

図 1-13に、CARRYINSEL プ ロ グ ラ ミ ン グ ビ ッ ト で選択 さ れた 2 つの入力を示 し ます。 最初の入

力 CARRYIN (CARRYINSEL は 0 に設定) は、 上位 DSP48A ブ ロ ッ ク のキ ャ リ ーア ウ ト で駆動 さ

れ ま す。2 つ目の入力は OPMODE[5] で、 一般的な ロ ジ ッ ク で駆動で き ま す。 こ のオプシ ョ ン は キ ャ リ ーフ ァ ン ク シ ョ ン の設定 を ユーザー ロ ジ ッ ク に基づい て実行す る か、 完全にDSP48A ブ ロ ッ ク に内在す る イ ンプ リ メ ン テーシ ョ ンか ら 実行 し ます。 こ の信号には、MREG パ イ プ ラ イ ン遅 延 と 一致す る よ う 、オプシ ョ ンで レ ジ ス タ を追加で き ます。 こ の レ ジ ス タ 遅延は CARRYINREG コ ン フ ィ ギ ュ レーシ ョ ン ビ ッ ト に よ り 制御 さ れます。

大規模乗算器の実現

図 1-14に、18 x 18 ビ ッ ト の小型乗算器に よ っ て構成 さ れ る 35 x 35 ビ ッ ト 乗算の構造を示 し ます。 「0,B[16:0]」 は、17 ビ ッ ト の B の値に符号ビ ッ ト と し て 0 の値がつけ ら れた 2 の補数形式で正の 値を表 し ます。 図 1-13 : 後置加算/減算器に供給 さ れるキ ャ リ ー入力ロ ジ ッ ク RST D QCarry Input (CIN) to Post-Adder/Subtracter CE RSTCARRYIN UG431_c1_12_011007 CARRYIN CLK OPMODE[5] 図 1-14 : 18 x 18 ビ ッ ト の乗算器によ っ て構成 さ れる 35 x 35 ビ ッ ト 乗算

AU = A[34:17]

Sign Extend 36 Bits of '0'

17-Bit Offset 34-Bit Offset

P[16:0]

UG431_c1_13_112706x BU = B[34:17]

AL = 0,A[16:0]

BL = 0,B[16:0]

BL * AL = 34 bits

[33:17] [16:0]

BL * AU = 35 bits

BU * AL = 35 bits

Sign Extend

18 Bits of B[34]

Sign Extend

18 Bits of A[34]

BU * AU = 36 bits

P[33:17]

P[51:34]

P[69:52]

[35:18] [17:0]

[34:17] [16:0]

[34:17] [16:0]

2 の補数を 2 つの部分に分割す る と 、 上位部分のみが元の符号を保持 し ます。 下位部分は符号が強 制的に 0 に さ れ る ため、 正のオペ ラ ン ド と な り ます。 正の値を 2 つの正の値に分割す る こ と は論理 的な よ う であ る 一方、 負の値を負の上位部分 と 正の下位部分に分割す る のは、 直感に反す る こ と か も し れません。 し か し 、 分割す る こ と に よ っ て、 上位部分の値は元の値 よ り 小 さ く な り 、 下位部分 の値は元の値 よ り 大 き く な っ てい ます。36 ビ ッ ト の入力オペ ラ ン ド には、下位部分に強制的に 0 に さ れた符号ビ ッ ト があ り ます。 し たがっ て入力オペ ラ ン ド 内の有効ビ ッ ト 数は 35 ビ ッ ト です。 18 x 18 乗算器お よ び後置加算/減算器付 き の DSP48A ス ラ イ ス は、図 1-14に示す部分積 4 つの合 計の イ ン プ リ メ ン ト に使用で き ま す。 下位の部分積は、 後続の上位の部分積に合算 さ れ る 前に 17 ビ ッ ト 分右方向へシ フ ト さ れます。 こ れは、C ポー ト に適用 さ れ、 ユーザーロ ジ ッ ク に イ ンプ リ メ ン ト さ れた ワ イ ヤ シ フ ト で実行 さ れ ます。70 ビ ッ ト の結果生成のため、 加算器カ ス ケー ド を使用 し た乗算、 シ フ ト 、 加算の全プ ロ セ ス を DSP48A ス ラ イ ス の専用回路で実現で き 、 最高の性能 と 低 消費電力を達成 し ます。

FIR

フ ィ ル タ

基本的な

FIR

フ ィ ル タ

FIR フ ィ ル タ は、映像放送お よ び ワ イ ヤ レ ス通信の分野で広 く 使用 さ れてい ます。DSP フ ィ ル タ ア プ リ ケーシ ョ ンには、 次が含まれます。 • ワ イ ヤ レ ス通信 • 画像処理 • 映像のフ ィ ルタ リ ン グ • マルチ メ デ ィ アアプ リ ケーシ ョ ン • 携帯型 ECG (心電図) デ ィ ス プ レ イ • GPS (グ ロ ーバルポジシ ョ ニ ン グシ ス テ ム) 数式1-4に、 シ ン グルチ ャ ネル FIR フ ィ ル タ の数式を示 し ます。 数式1-4

こ の数式の項は、 入力サン プル、 出力サン プル、 お よ び係数です。x が連続 し て入力 さ れ る 入力サ ンプルで、y が出力サンプルの一連の出力結果だ と し ます (フ ィ ル タ さ れた出力結果)。 数式の n お よ び k は、 特定の時刻 と 対応 し てい ます。 し たが っ て出力サン プル y(n) を n の タ イ ミ ン グで処理 す る には、N 個の異な る 時刻での入力サンプル x(n)、x(n-1)、x(n-2)、… x(n-N+1) が必要です。 一 連の N 個の入力サンプルは N 個の係数で乗算 さ れ、 それ ら の合計が最終結果 y と な り ます。 デジ タ ルフ ィ ル タ アルゴ リ ズ ムの イ ンプ リ メ ン ト に使用 さ れ る 主な コ ン ポーネ ン ト には、 加算器、 乗算器、 ス ト レージ、 お よ び遅延エ レ メ ン ト が含まれます。DSP48A ス ラ イ スは こ れ ら のエ レ メ ン ト すべて を含み、 デジ タ ルフ ィ ル タ 機能の イ ンプ リ メ ン ト に最適です。 一連の n サンプルか ら の入 力サンプルは、 各 DSP48A ス ラ イ ス の入力に送信 さ れます。 各ス ラ イ ス は、 こ れ ら のサンプルを対 応す る 係数で乗算 し ます。 乗算器の出力は、 カ ス ケー ド 接続 さ れた加算器に結合 さ れます。 図 1-15では、 サンプル遅延 ロ ジ ッ ク を Z-1で示 し ます。–1 は 1 ク ロ ッ クサ イ ク ルの遅延を示 し ま す。遅延 し た入力サンプルは乗算器の入力の 1 つに送信 さ れます。h0 ∼ h(N-1) で示す係数は、個々の ROM、RAM、 レ ジ ス タ ま たは定数を介 し て乗算器の も う 一方の入力に送信 さ れます。Y(n) は、

一連の入力サンプルを各係数 と 乗算 し た値の合計です。 y n( ) h k( )x n k( – ) k=0 k=N–1

∑

=マルチチ ャ ネル

FIR

フ ィ ル タ

マルチチ ャ ネルフ ィ ル タ は、 複数チ ャ ネルの入力デー タ を処理す る ためのフ ィ ル タ です。 各チ ャ ネ ルは同 じ 係数のセ ッ ト 、 ま たは異な る 係数のセ ッ ト のいずれか を使用で き ます。 マルチチ ャ ネルフ ィ ル タ の一般的な例 と し て、 無線受信機のデジ タ ルダ ウ ン コ ンバー タ があ り ま す。数式1-5に数式を、図 1-16にブ ロ ッ ク 図を示 し ます。 デジ タ ル化 さ れたベースバン ド 信号は、 マ ッ チ ド ロ ーパ ス フ ィ ル タ M(z) に送信 さ れ、 デー タ レ ー ト が入力サ ン プル レ ー ト か ら ビ ッ ト レ ー ト に低減 さ れ ま す。 結果 と し て現れ る イ ン フ ェ ーズお よ び直交位相信号は、 それぞれが同 じ フ ィ ル タ で処理 さ れ る ため、 サン プルレー ト の 2 倍速で駆動す る マルチチ ャ ネル フ ィ ル タ 1 つで 処理可能です。 x(n) = xI(n) + jxQ(n) 数式1-5

して ビデオ アプ リ ケーシ ョ ンには、 ビデオ ス ト リ ームの複数 コ ン ポーネ ン ト にマルチチ ャ ネルフ ィ ル タ を使用す る も のがあ り ます。 一般的な ビデオ コ ン ポーネ ン ト には、 赤、 緑、 青 (RGB) ま たは輝 度、 赤の色素、 青の色素 (YCrCb) があ り ます。 異な る ビデオ コ ン ポーネ ン ト は、 係数 ROM の構 成を変更す る だけで、 チ ャ ネルご と に同 じ 係数ま たは異な る 係数を処理で き ます。FIR

フ ィ ル タ の作成

図 1-6、表 1-4、 お よ び表 1-5に示す よ う に、P レ ジ ス タ に最初のオペ ラ ン ド を ロ ー ド す る こ と で、 内部積 MACC 動作が開始 し ます。 乗算器の出力は X マルチプ レ ク サを使用 し て渡 さ れ、0 と 加算 さ れて P レ ジ ス タ に ロ ー ド さ れ ます。 値が00000001の読み込み動作 OPMODE では、Z マルチ 図 1-15 : 従来の タ ッ プ遅延ラ イ ン FIR フ ィ ル タ ug431_c1_14_112706 Z-1 Z-1 Z-1 Z-1 Z-1 x(n) y(n) h(0)×

h(1)×

h(2) h(3)×

×

h(4)×

h(N-1)×

+ + + + +

図 1-16 : ソ フ ト ウ ェ ア指定の無線デジ タ ルダウン コ ンバー タ ug431_c1_15_112706 v(n) xl(n) xQ(n) I Q M(z) M(z)Direct Digital Synthesizer (DDS)

![表 1-7 に、 すべての DSP48A 動作モー ド を示 し ます。 表 1-7 : DSP48A 動作モー ド OPMODE OPMODE[7:0] CARRYINSEL 出力後置加算/減算器前置加算/減算器CARRYIN前置加算/減算器セレクトZX 7 6 5 4 3 2 1 0 0 + CARRYIN 0 0/1 0/1 0/1 0 0 0 0 0 + CARRYIN 0 – CARRYIN 1 0/1 0/1 0/1 0 0 0 0 0 – CARRYIN 0 + OPMODE<5](https://thumb-ap.123doks.com/thumbv2/123deta/5983054.575904/29.892.69.826.160.1048/すべて動作モー動作モーCARRYINSEL出力後置加算減算器前セレクトZX+CARRYIN.webp)