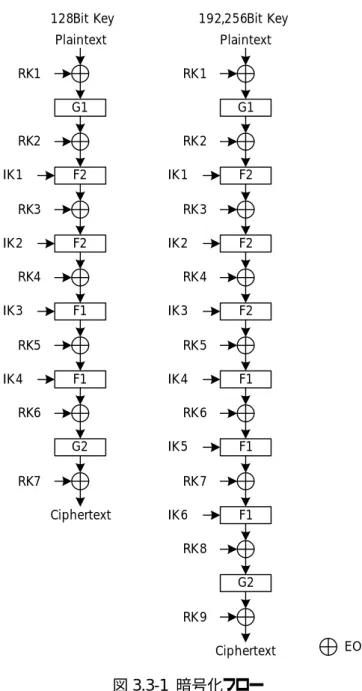

HyRAL®FPGA設計仕様書

61

0

0

全文

図

![図 3.4.1-1 内のY0~3 は入力する 128bitデータを意味し、Y0=Y[127:96], Y1=Y[95:64], Y2=Y[63:32], Y3=Y[31:0]を意味する。同様に、IKi0=IKi[127:96], IKi1= IKi[95:64], IKi2= IKi[63:32], IKi3= IKi[31:0]を意味 する。X0~3 はX0=X[127:96], X1=X[95:64], X2=X[63:32], X3=X[31:0]を意味し、F - 関数の出力である。](https://thumb-ap.123doks.com/thumbv2/123deta/6778885.721594/17.892.205.775.242.771/データYYY意味する同様IKiIKiIKiIKiIKi=IKiIKi=IKiX出力ある.webp)

+2

Outline

関連したドキュメント

お客様は、各ASLロケーションにおいて、マスター・インストール・メデ ィア及びApproved Volume License

原稿は A4 判 (ヨコ約 210mm,タテ約 297mm) の 用紙を用い,プリンターまたはタイプライターによって印 字したものを原則とする.

本手順書は複数拠点をアグレッシブモードの IPsec-VPN を用いて FortiGate を VPN

ダウンロードした書類は、 「MSP ゴシック、11ポイント」で記入で きるようになっています。字数制限がある書類は枠を広げず入力してく

※お寄せいた だいた個人情 報は、企 画の 参考およびプ レゼントの 発 送に利用し、そ れ以外では利

キャンパスの軸線とな るよう設計した。時計台 は永きにわたり図書館 として使 用され、学 生 の勉学の場となってい たが、9 7 年の新 大

・電源投入直後の MPIO は出力状態に設定されているため全ての S/PDIF 信号を入力する前に MPSEL レジスタで MPIO を入力状態に設定する必要がある。MPSEL

3) Sato T, Kase Y, Watanabe R, Niita K, et al: Biological Dose Estimation for Charged-Particle Therapy Using an Improved PHITS Code Coupled with a Microdosimetric Kinetic

![図 3.4.2-1 内のX0~3 は入力する 128bitデータを意味し、Y0=Y[127:96], Y1=Y[95:64], Y2=Y[63:32], Y3=Y[31:0]を意味する。Y0~3 はX0=X[127:96], X1=X[95:64], X2=X[63:32], X3=X[31:0]Y0=Y[127:96], Y1=Y[95:64], Y2=Y[63:32], Y3=Y[31:0]を意味し、G - 関数の出力である。](https://thumb-ap.123doks.com/thumbv2/123deta/6778885.721594/18.892.224.768.250.777/データ意味YYYYYYするYXXXXXXYYYYYY出力ある.webp)