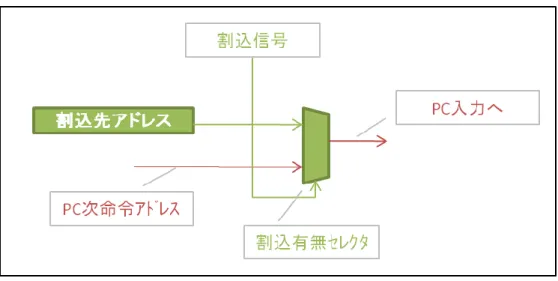

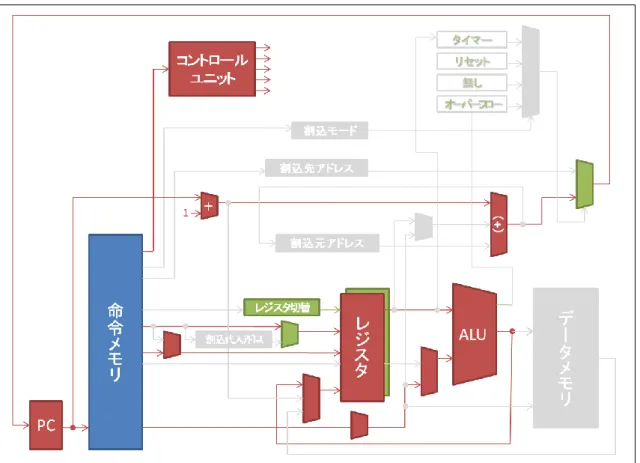

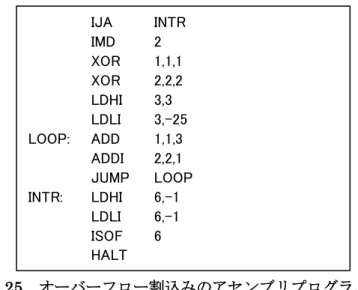

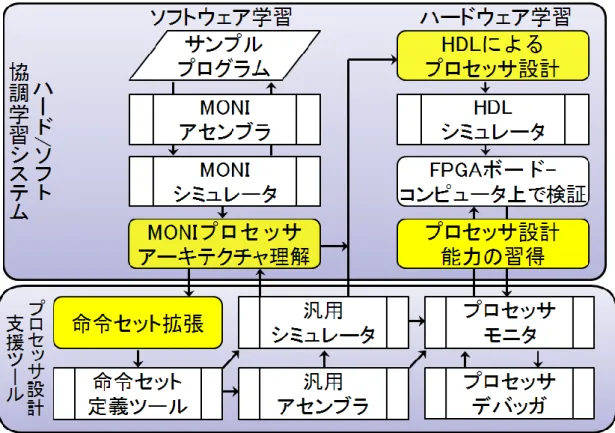

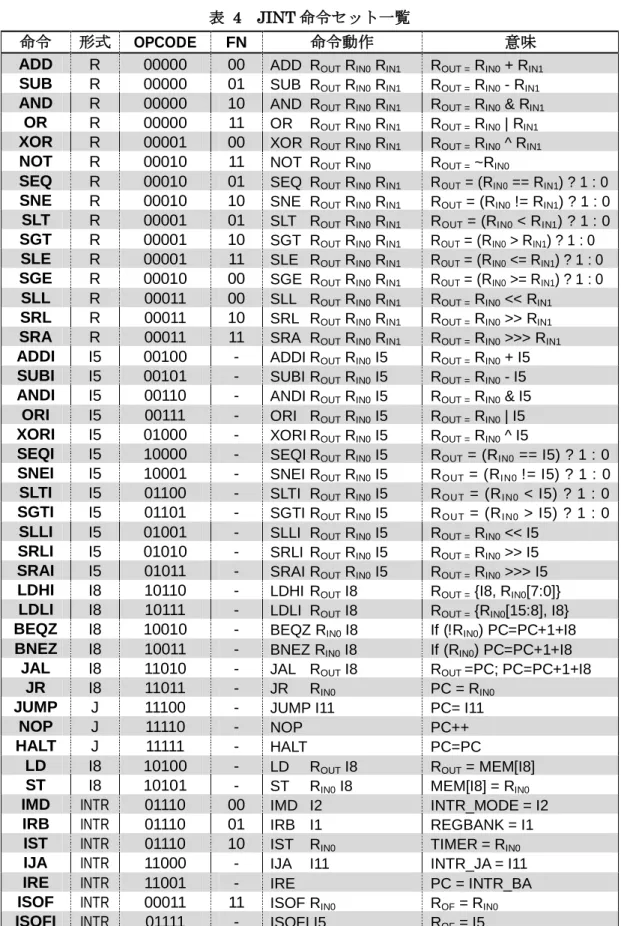

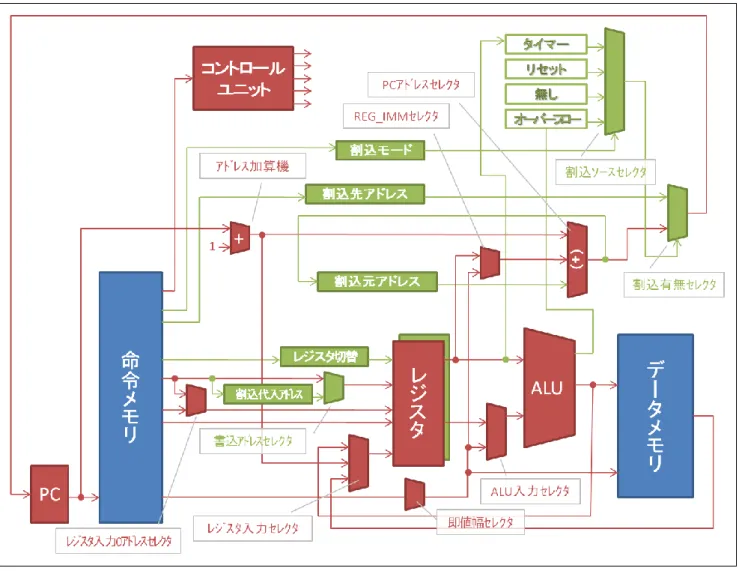

内容概要本論文では 割込みの目的や原理を理解するとともに ハード / ソフト協調学習システムを用いて割込みプロセッサを設計することで ハードウェアとソフトウェアの両方の観点から知識を得ることを目的とし Verilog HDL によるシングルサイクルの割込みプロセッサを設計した 設計したプロセッサは

39

0

0

全文

図

+7

Outline

関連したドキュメント

パスワード 設定変更時にパスワードを要求するよう設定する 設定なし 電波時計 電波受信ユニットを取り外したときの動作を設定する 通常

充電器内のAC系統部と高電圧部を共通設計,車両とのイ

工場設備の計測装置(燃料ガス発熱量計)と表示装置(新たに設置した燃料ガス 発熱量計)における燃料ガス発熱量を比較した結果を図 4-2-1-5 に示す。図

本文書の目的は、 Allbirds の製品におけるカーボンフットプリントの計算方法、前提条件、デー タソース、および今後の改善点の概要を提供し、より詳細な情報を共有することです。

ASTM E2500-07 ISPE は、2005 年初頭、FDA から奨励され、設備や施設が意図された使用に適しているこ

キャンパスの軸線とな るよう設計した。時計台 は永きにわたり図書館 として使 用され、学 生 の勉学の場となってい たが、9 7 年の新 大

現状では、3次元CAD等を利用して機器配置設計・配 管設計を行い、床面のコンクリート打設時期までにファ

「JSME S NC-1 発電用原子力設備規格 設計・建設規格」 (以下, 「設計・建設規格」とい う。