Copyright©2015 Gigafirm Co.,Ltd. All Rights Reserved 1

GF43 ACA DE MINO 扱 明書

GF43 ACA DE MINO

扱 明書

Version 1.03

2015/09/011 Gigafirm

Copyright©2015 Gigafirm Co.,Ltd. All Rights Reserved 2

GF43 ACA DE MINO 扱 明書

Table of contents

1 製品概要 ... 4

1.1 機能概要 ... 4

1.2 製品外観 ッ 図 ... 5

1.3 開 環境 ... 7

2 セッ ッ ... 8

2.1 電源 供給方法 ... 8

2.1.1 AP203/AS501 共通 ... 8

2.2 電源系統図 ... 10

2.3 コ 出力電源 ... 11

2.4 コ へ 電源供給設定 ... 12

2.4.1 FMC コ ... 12

2.4.2 Arduino コ ... 13

3 機能 明 ... 18

3.1 セッ ... 19

3.2 ッ 系統 ... 21

3.3 PCI Express ... 24

3.3.1 PCI Express ッ コ ン配置 CN1 ... 24

3.3.2 PCI Express コ FPGA 間 接続 ン番号 ... 25

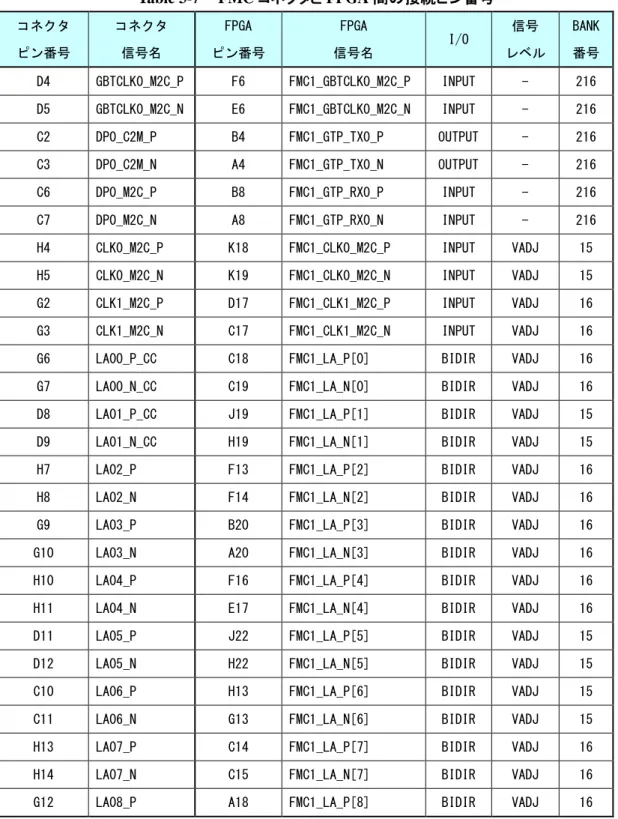

3.4 FMC コ LPC:CN2 ... 26

3.4.1 FMC コ LPC ン配置 ... 26

3.4.2 FMC コ FPGA 間 接続 ン番号 ... 27

3.5 Arduino コ CN6-CN9 ... 30

3.5.1 Arduino コ ン配置 ... 30

3.5.2 Arduino コ FPGA 間 接続 ン番号 ... 32

3.5.3 Arduino コ ッ 制御 IO ... 35

3.5.4 Arduino 入力 ... 36

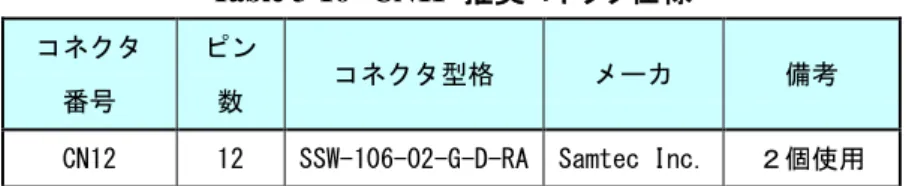

3.6 FPGA 拡張 IO CN ... 37

3.6.1 FPGA 拡張 IO ン配置 ... 37

3.6.2 FPGA 拡張 IO FPGA 間 接続 ン番号 ... 39

3.7 DDR3 ... 40

3.7.1 DDR3 SDRAM FPGA 間 接続 ン番号 ... 40

3.8 HDMI コ CN12 ... 42

3.8.1 HDMI コ ン配置 ... 42

3.8.2 HDMI コ FPGA 間 接続 ン番号 ... 43

3.9 U.FL コ CN13 ~ CN16 ... 44

Copyright©2015 Gigafirm Co.,Ltd. All Rights Reserved 3

GF43 ACA DE MINO 扱 明書

3.9.1 U.FL コ FPGA 間 接続 ン番号 ... 44

3.10 SATA コ ... 45

3.10.1 SATA コ ン配置 ... 45

3.10.2 FPGA 接続 ン番号 ... 45

3.11 7 seg.LED ... 46

3.11.1 7seg.LED FPGA 間 接続 ン番号 ... 47

3.12 STATUS LED ... 48

3.12.1 STATUS LED FPGA 間 接続 ン番号 ... 48

3.13 DIPSW ... 48

3.13.1 DIPSW FPGA 間 接続 ン番号 ... 48

3.14 PUSH SW ... 49

3.14.1 専用 PUSH SW ... 49

3.14.2 用 PUSW SW FPGA 間 接続 ン番号 ... 49

注意事項

利用 際 静電気対策 し 利用し い

接続 送信 信 接続 間違え い う 注意し い

外観 び 様 予告 変更 場合 あ

本書記載 会社 製品 各社 商標 録商標

Copyright©2015 Gigafirm Co.,Ltd. All Rights Reserved 4

GF43 ACA DE MINO 扱 明書

1 製品概要

ACADEMINO Arduino 用 FPGA

ッ 開 用 利用 う 拡張性 コンセ し ン ソ

製品や 高速 ン 付 可能

本製品 搭載 い FPGA や 機能 以 種類 製品 あ

AP203 Professional model

AS501 Standard model

1.1 機能概要

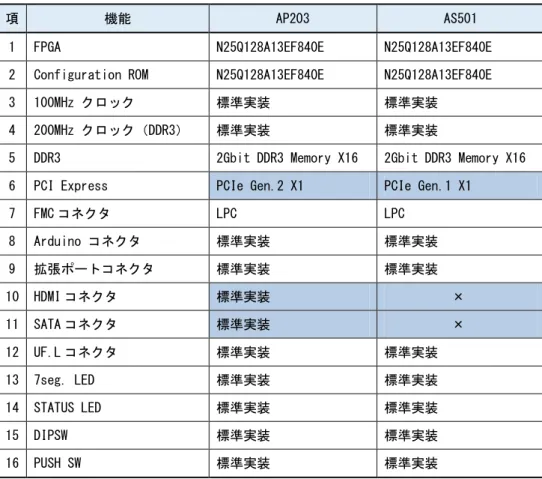

Table 1-1 本 機能概要 び AP203/AS501 違い 示し

Table 1-1 Academino 機能概要

項 機能 AP203 AS501

1 FPGA N25Q128A13EF840E N25Q128A13EF840E 2 Configuration ROM N25Q128A13EF840E N25Q128A13EF840E

3 100MHz ッ 標準実装 標準実装

4 200MHz ッ DDR3 標準実装 標準実装

5 DDR3 2Gbit DDR3 Memory X16 2Gbit DDR3 Memory X16 6 PCI Express PCIe Gen.2 X1 PCIe Gen.1 X1

7 FMCコネ タ LPC LPC

8 Arduino コネ タ 標準実装 標準実装

9 拡張 ー コネ タ 標準実装 標準実装

10 HDMIコネ タ 標準実装 ×

11 SATAコネ タ 標準実装 ×

12 UF.Lコネ タ 標準実装 標準実装

13 7seg. LED 標準実装 標準実装

14 STATUS LED 標準実装 標準実装

15 DIPSW 標準実装 標準実装

16 PUSH SW 標準実装 標準実装

Copyright©2015 Gigafirm Co.,Ltd. All Rights Reserved 5

GF43 ACA DE MINO 扱 明書

1.2 製品外観と ロッ 図

[AP203]

以 AP203 外観図 示し

Figure 1-1 AP203 外観図

Figure 1-2 AP203 ッ 図

Copyright©2015 Gigafirm Co.,Ltd. All Rights Reserved 6

GF43 ACA DE MINO 扱 明書

[AS501]

以 AS501 外観図 示し

Figure 1-3 AS501 外観図

Figure 1-4 AS501 ッ 図

Copyright©2015 Gigafirm Co.,Ltd. All Rights Reserved 7

GF43 ACA DE MINO 扱 明書

1.3 開発環境

本 搭載 い FPGA 開 環境 以 示し

本 以 開 環境 使用し 確認し い

Xilinx VIVADO 2014.4

Copyright©2015 Gigafirm Co.,Ltd. All Rights Reserved 8

GF43 ACA DE MINO 扱 明書

2 セッ ッ

本 使用 セッ ッ 内容 い 明し

2.1 電源の供給方法

本 へ 電源供給方法 い 以 明し

2.1.1 AP203/AS501 共通

AP203/AS501 以 方法 電源 供給し

AC 供給 方法

コ CN4 付属 AC (DC +12V) 接続し い そし 電源

ッ SW1 +12VIN 側 電源 供給

Figure 2-1 AC 電源供給

AC CN4 接続

電源 ON

Copyright©2015 Gigafirm Co.,Ltd. All Rights Reserved 9

GF43 ACA DE MINO 扱 明書

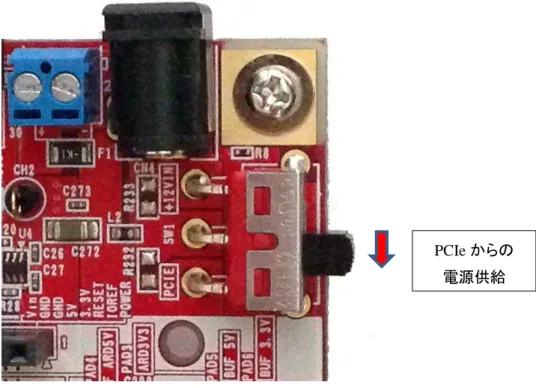

PCI Express 供給 方法

電源 ッ SW1 PCIE 側 PCI Express 電源 供給

う 本状態 PC PCI Express 挿入し い

Figure 2-2 PCI Express 電源供給

PCIe

電源供給

Copyright©2015 Gigafirm Co.,Ltd. All Rights Reserved 10

GF43 ACA DE MINO 扱 明書

2.2 電源系統図

Figure 2-3 本 電源系統図 示し

ADP5052 +12V

VCCINT (+1.0V:max 2A)

VCCAUX (+1.8V:max 0.5A) +3.3V:max 1.2A

+1.5V (DDR):max 1.2A

ADP125

MGTAVTT (+1.2V:max 0.2A)

TPS51200

VTT (+0.75V:max 3.0A)

FPGA

ADP2303

+5.0V:max 3A Alduino/Buffer

DDR3 VADJ:max 3A

+3.3V

MGTAVCC (+1.0V:max 0.5A) CH5

CH1 CH2 CH3 CH4

ADP125

VREF(+0.75V:max 0.5A)

FMC +1.5V

VTT VREF

VADJ +3.3V

+12V

+3.3V +12V

CN5 +12V

Figure 2-3 電源系統図

Copyright©2015 Gigafirm Co.,Ltd. All Rights Reserved 11

GF43 ACA DE MINO 扱 明書

2.3 コネ タ出力電源

本 FMC/Arsuino/ 拡張 IO コ 電源 供給 可能

Table 2-1 示 各電源 最大電流容量 超え い う し い

各電源 内部 使用し い 電源系統図 内部 外部 両方

電流容量 考慮し い

Table 2-1 最大電流容量

電源 電 値 出力コネ タ 電流容量 備考

+12V +12V 外部電源出力/Arduino コネ タ - 注

+5V +5V Arduino コネ タ 3A

+3.3V +3.3V FMC コネ タArduino コネ タ/拡張コネ タ 1.2A

VADJ VADJ FMC コネ タ 4A

注 +12V 電流容量 接続 電源 AC or PCIe

Copyright©2015 Gigafirm Co.,Ltd. All Rights Reserved 12

GF43 ACA DE MINO 扱 明書

2.4 コネ タへの電源供給設定

FMC/Arduino コ 出力 電源 い 接続 ン 合わ

設定 必要 あ

2.4.1 FMC コネ タ

FMC コ VADJ 電源 PAD8/PAD9 電源電圧 設定し

Table 2-2 設定内容 示し

FMCコ 使用し い場合 必 設定し い 両方 ン

状態 FPGA 壊 可能性 あ

Table 2-2 VADJ 出力電圧設定

PAD PAD名 電源名 内容

出荷時 設定

備考 AP203 AS501

PAD8 VADJ 2.5V

VADJ

FMC コネ タ VADJ 電源を +2.5V に設定す

OPEN OPEN PAD8,PAD9 、

一つ け ョー す

うにし く さい

PAD9 VADJ 3.3V

FMC コネ タ VADJ 電源を

+3.3V に設定す SHORT SHORT

Figure 2-4

PAD8:VADJ 2.5V PAD9:VADJ 3.3V

Copyright©2015 Gigafirm Co.,Ltd. All Rights Reserved 13

GF43 ACA DE MINO 扱 明書

2.4.2 Arduino コネ タ

Arduino コ 出荷時 標準実装 い 以 推奨コ 様 示し

Table 2-3 Arduino コ 様

コネ タ

番号

ン 数

コネ タ型格 ーカ 備考

CN6 8 SSQ-108-04-L-S Samtec Inc. CN7 8 SSQ-108-04-L-S Samtec Inc. CN8 10 SSQ-110-04-L-S Samtec Inc. CN9 6 SSQ-106-04-L-S Samtec Inc.

Figure 2-5 Arduino コ 実装状態

Copyright©2015 Gigafirm Co.,Ltd. All Rights Reserved 14

GF43 ACA DE MINO 扱 明書

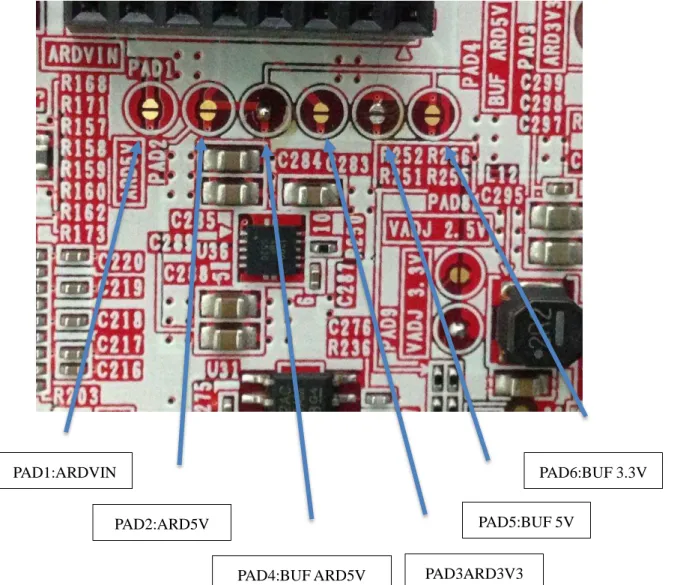

次 Arduino コ 供給 電源 PAD1-PAD7 設定し 接続

設定 切 替え 使用し い

Arduino 使用 設定 行う PAD 一覧 Table 2-4 示し

Table 2-4 Arduino コ 電源設定一覧

PAD PAD名 電源名 内容

出荷時 設定

備考 AP203 AS501

PAD1 ARDVIN VIN Arduino

コネ タ VIN 端子 に+12V を供給

OPEN OPEN 注1

PAD2 ARD5V +5V

Arduino コネ タ 5V 端子に

+5V を供給 OPEN OPEN

注1

PAD3 ARD3V3 +3.3V

Arduino コネ タ 3.3V 端子

に+3.3V を供給

OPEN OPEN 注1

PAD4 BUF ARD5V

ARD_BUFVCC

Arduino コネ タ FPGA 間に

あ バッ 、Arduino 側 電源を Arduino ー +5V 電源に設定します

SHORT SHORT

PAD4,PAD5,PAD6

一つ け ョー

す うにし く さい

PAD5 BUF 5V

Arduino コネ タ FPGA 間に

あ バッ 、Arduino 側 電源を ー 上 +5V 電源に 設定します

OPEN OPEN

PAD6 BUF 3.3V

Arduino コネ タ FPGA 間に

あ バッ 、Arduino 側

電源を ー 上 +3.3V 電源 に設定します

OPEN OPEN

PAD7 DDR5V ARD_BUFVCCA

FPGA BANK34/BANK35 VCCO電 を +3.3V に設定

します

OPEN OPEN 注

Copyright©2015 Gigafirm Co.,Ltd. All Rights Reserved 15

GF43 ACA DE MINO 扱 明書

Figure 2-6 Arduino 電源設定 PAD

PAD1:ARDVIN PAD6:BUF 3.3V

PAD2:ARD5V PAD5:BUF 5V

PAD4:BUF ARD5V PAD3ARD3V3

Copyright©2015 Gigafirm Co.,Ltd. All Rights Reserved 16

GF43 ACA DE MINO 扱 明書

以 標準的 Arduino 使用 電源設定例 示し

注 Arduino 以 設定 合わ い場合 あ 必 電源

確認し そ 合わ 設定し い

MPU 場合

Arduino MUP 場合 電源 搭載し い ほ

MPU 本基板 電源 供給 う 設定し

ー PAD1 PAD2 PAD3 PAD4 PAD5 PAD6 PAD7 備考

AP203 注 OPEN OPEN SHORT OPEN OPEN OPEN AS501 注 OPEN OPEN SHORT OPEN OPEN OPEN

IO SHIELD 場合

Arduino SHIELD 直接本 接続し 使用 場合 以 設定

使用 推奨し し SHIELD +5V 入力動作 い場合

適切 電源設定 し 頂 願い致し 例 し +3.3V 動作 時 そ

項 参照

ー PAD1 PAD2 PAD3 PAD4 PAD5 PAD6 PAD7 備考

AP203 注 SHORT OPEN OPEN SHORT OPEN OPEN AS501 注 SHORT OPEN OPEN SHORT OPEN OPEN

そ

+3.3V 動作 SHIELD や 自作 +3.3V 動作 SHIELD 使用

場合 以 設定 使用 推奨し

ー PAD1 PAD2 PAD3 PAD4 PAD5 PAD6 PAD7 備考

AP203 注 OPEN SHORT OPEN OPEN SHORT OPEN AS501 注 OPEN SHORT OPEN OPEN SHORT OPEN

Copyright©2015 Gigafirm Co.,Ltd. All Rights Reserved 17

GF43 ACA DE MINO 扱 明書

注 PAD1-PAD3 し 使用 場合 Arduino 側 絶対

電源 接続し い い 壊 し い

注 PAD7 (DDR BANK) い 壊 SHORTし

使用し い い

注 PAD1 (VIN) Arduino +12V 供給可能

MPU う 消費電流 大 い 本端子 使用

直接電源 供給し 使用 う し い

Copyright©2015 Gigafirm Co.,Ltd. All Rights Reserved 18

GF43 ACA DE MINO 扱 明書

3 機能説明

本性 本 搭載 い 機能 び搭載可能 機能 い 明し

Figure 3-1 搭載機能

JTAG HDMI 拡張 IO コ

7seg LED

DIPSW

FMC

SATA

PCI Express

DDR3

Arduino

LED

U.FL

Arduino

Push SW

RESET SW

Config SW

Copyright©2015 Gigafirm Co.,Ltd. All Rights Reserved 19

GF43 ACA DE MINO 扱 明書

3.1 セッ

本 FPGA 作成 ワ ン セッ ッ

セッ PCI Express セッ Arduino コ セッ 回路 セッ

行う

PCI Express セッ 単独 入力 い PCI Express Core へ

セッ 本信号 使用 推奨し

以 本 セッ 系統図 び端子表 示し

注 Arduinoコ 単独 接続し 使用 時 Arduino側 セッ

信号 ッ い い場合 セッ 解除 い状況 生し

本状況 回避 ARD_RESET_CNT = „0‟ 出力 う 回路

作成し FPGA コン ン終了後 Arduino 側 セッ 行う う し

い

FPGA

LVC07

ADM6713 PCIe Bus

Arduino TXB0101

OE A B

RESET MR +3.3V

+3.3V

ARD_RESET PCIE_RESETN

ARD_RESET_CNT (240ms)

Figure 3-2 セッ 系統図

Copyright©2015 Gigafirm Co.,Ltd. All Rights Reserved 20

GF43 ACA DE MINO 扱 明書

Table 3-1 セッ 入力端子表

FPGAン番号

FPGA

信号名

I/O

信号 ベ

BANK

番号 U20 PCIE_RESETN INPUT LVCMOS33 14 Y22 ARD_RESET BIDIR LVCMOS33 14

Copyright©2015 Gigafirm Co.,Ltd. All Rights Reserved 21

GF43 ACA DE MINO 扱 明書

3.2 ロッ 系統

本 以 Table 3-2 示 ッ 使用可能

Table 3-2 ッ 入力一覧表

CLOCK信号名称 内容 備考

MGTREFCLK1_P MGTREFCLK1_N

PCIe BUS ン ッ

100MHz

MGTREFCLK0_P MGTREFCLK0_N

FMC カー GTP 用 ン ッ C92/C93:実装

C320/C321:未実装

ー 上 200MHz 発振器 入力 C92/C93:未実装

C320/C321:実装 SYS_CLK_P

SYS_CLK_N

ー 上 200MHz 発振器 入力

DDR3用 ッ

FMC1_CLK0_M2C_P FMC1_CLK0_M2C_N FMC1_CLK1_M2C_P FMC1_CLK1_M2C_N

FMC カー ッ 入力

FPGA_DIFF_IO0_P FPGA_DIFF_IO0_N FPGA_DIFF_IO1_P FPGA_DIFF_IO1_N

UF.L コネ タ 入力、 び出力

ン エン /差動 も可

FPGA_CLKIN ー 上 100MHz 発振器 入力

注 MGTREFCLK0_P/MGTREFCLK1_N ッ FMC ッ

ッ 切 替え う い 時 使用し い

う し い

Copyright©2015 Gigafirm Co.,Ltd. All Rights Reserved 22

GF43 ACA DE MINO 扱 明書

以 本 ッ 系統図 示し

PCIe Bus FPGA

MGTREFCLK1_P MGTREFCLK1_N PCIE_REFCLK_P

PCIE_REFCLK_N

FMC

MGTREFCLK0_P MGTREFCLK0_N FMC1_GBTCLK0_M2C_P

FMC1_GBTCLK0_M2C_N

C92

C93

C320

C321

MGTREFCLK1P_216 MGTREFCLK1N_216

MGTREFCLK0P_216 MGTREFCLK0N_216

SYS_CLK_P SYS_CLK_N 発 振 器

200MHz

発 振 器

100MHz

FMC1_CLK0_M2C_P FMC

FMC1_CLK0_M2C_N

FMC1_CLK1_M2C_P FMC1_CLK1_M2C_N

FPGA_CLKIN

IO_L12P_T1_MRCC_14 IO_L13N_T2_MRCC_15 IO_L13P_T2_MRCC_15

IO_L12N_T2_MRCC_16 IO_L12P_T2_MRCC_16 IO_L13N_T2_MRCC_34 IO_L13P_T2_MRCC_34

FPGA_DIFF_IO0_P UF.L

FPGA_DIFF_IO0_N

FPGA_DIFF_IO1_P FPGA_DIFF_IO1_N

IO_L14N_T2_SRCC_16 IO_L14P_T2_SRCC_16 IO_L11N_T2_SRCC_16 IO_L11P_T2_SRCC_16 IO0+

IO0-

IO1+ IO1-

Figure 3-3 ッ 系統図

Copyright©2015 Gigafirm Co.,Ltd. All Rights Reserved 23

GF43 ACA DE MINO 扱 明書

Table 3-3 ッ 入力端子表

FPGAン番号

FPGA

信号名

I/O

信号 ベ

BANK

番号

F10 MGTREFCLK1_P INPUT ー 216

E10 MGTREFCLK1_N INPUT ー 216

F6 MGTREFCLK0_P INPUT ー 216

E6 MGTREFCLK0_N INPUT ー 216

R4 SYS_CLK_P INPUT LVDS 34

T4 SYS_CLK_N INPUT LVDS 34

K18 FMC1_CLK0_M2C_P INPUT VADJ 16 K19 FMC1_CLK0_M2C_N INPUT VADJ 16 D17 FMC1_CLK1_M2C_P INPUT VADJ 15 C17 FMC1_CLK1_M2C_N INPUT VADJ 15 B17 FPGA_DIFF_IO0_P BIDIR VADJ 16 B18 FPGA_DIFF_IO0_N BIDIR VADJ 16 E19 FPGA_DIFF_IO1_P BIDIR VADJ 16 D19 FPGA_DIFF_IO1_N BIDIR VADJ 16 W19 FPGA_CLKIN INPUT LVCMOS33 14

Copyright©2015 Gigafirm Co.,Ltd. All Rights Reserved 24

GF43 ACA DE MINO 扱 明書

3.3 PCI Express

本 FPGA 内蔵 い PCI Express IP 使用 PCI Express

ン 機能 使用

FPGA 内蔵 PCI Express IP い 以 資料 参照し い

pg054-7series-pcie.pdf

3.3.1 PCI Express カー エッジコネ タ ン配置 CN1

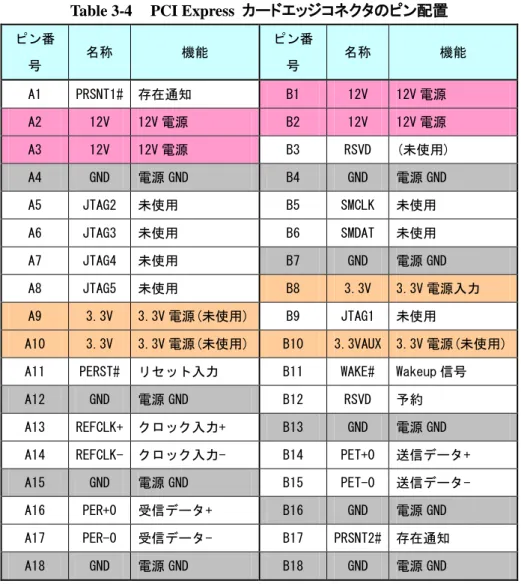

Table 3-4 PCI Express ッ コ ン配置 示し

Table 3-4 PCI Express ッ コ ン配置

ン番 号

名称 機能

ン番 号

名称 機能

A1 PRSNT1# 存 通知 B1 12V 12V電源

A2 12V 12V電源 B2 12V 12V電源

A3 12V 12V電源 B3 RSVD (未使用)

A4 GND 電源GND B4 GND 電源GND

A5 JTAG2 未使用 B5 SMCLK 未使用

A6 JTAG3 未使用 B6 SMDAT 未使用

A7 JTAG4 未使用 B7 GND 電源GND

A8 JTAG5 未使用 B8 3.3V 3.3V電源入力

A9 3.3V 3.3V電源(未使用) B9 JTAG1 未使用

A10 3.3V 3.3V電源(未使用) B10 3.3VAUX 3.3V電源(未使用) A11 PERST# セッ 入力 B11 WAKE# Wakeup信号

A12 GND 電源GND B12 RSVD 予約

A13 REFCLK+ ッ 入力+ B13 GND 電源GND A14 REFCLK- ッ 入力- B14 PET+0 送信 ータ+

A15 GND 電源GND B15 PET-0 送信 ータ-

A16 PER+0 受信 ータ+ B16 GND 電源GND

A17 PER-0 受信 ータ- B17 PRSNT2# 存 通知

A18 GND 電源GND B18 GND 電源GND

Copyright©2015 Gigafirm Co.,Ltd. All Rights Reserved 25

GF43 ACA DE MINO 扱 明書

3.3.2 PCI Express コネ タと FPGA 間の接続 ン番号

Table 3-5 PCI Express ッ コ FPGA 間 接続 ン 示し

Table 3-5 PCI Express FPGA 間接続信号

コネ タ

ン番号

コネ タ

信号名

FPGA

ン番号

FPGA

信号名

I/O

信号 ベ

BANK

番号

B14 PET+0 D7 pci_exp_txp[0] OUTPUT

B15 PET-0 C7 pci_exp_txn[0] OUTPUT

A16 PER+0 D9 pci_exp_rxp[0] INPUT

A17 PER-0 C9 pci_exp_rxn[0] INPUT

A13 REFCLK+ F10 pcie_sys_clk_p INPUT

A14 REFCLK- E10 pcie_sys_clk_n INPUT

A11 PERST# U20 pcie_sys_rst_n INPUT LVCMOS33 14 B11 WAKE# V20 pcie_wake_on OUTPUT LVCMOS33 14

Copyright©2015 Gigafirm Co.,Ltd. All Rights Reserved 26

GF43 ACA DE MINO 扱 明書

3.4 FMC コネ タ LPC:CN2

本 ANSI/VITA 57(Version1.1) LPC 対応し FMC コ 搭載し い

本規格 対応し 接続し 使用

3.4.1 FMC コネ タ LPC ン配置

Table 3-6 FMC コ ン配置 示し

Table 3-6 FMC コ LPC ン配置

No. H G D C No.

1 VREF_A_M2C FMC1_VREF_A GND DG PG_C2M ARD_RESET GND DG 1

2 PRSNT_M2C_L DG CLK1_M2C_P CLK1_P GND DG DP0_C2M_P GTP_TX_P 2

3 GND DG CLK1_M2C_N CLK1_N GND DG DP0_C2M_N GTP_TX_N 3

4 CLK0_M2C_P CLK0_P GND DG GBTCLK0_M2C_P GTP_CLK_P GND DG 4

5 CLK0_M2C_N CLK0_N GND DG GBTCLK0_M2C_N GTP_CLK_N GND DG 5

6 GND DG LA00_P_CC I/O GND DG DP0_M2C_P GTP_RX_P 6

7 LA02_P I/O LA00_N_CC I/O GND DG DP0_M2C_N GTP_RX_N 7

8 LA02_N I/O GND DG LA01_P_CC I/O GND DG 8

9 GND DG LA03_P I/O LA01_N_CC I/O GND DG 9

10 LA04_P I/O LA03_N I/O GND DG LA06_P I/O 10

11 LA04_N I/O GND DG LA05_P I/O LA06_N I/O 11

12 GND DG LA08_P I/O LA05_N I/O GND DG 12

13 LA07_P I/O LA08_N I/O GND DG GND DG 13

14 LA07_N I/O GND DG LA09_P I/O LA10_P I/O 14

15 GND DG LA12_P I/O LA09_N I/O LA10_N I/O 15

16 LA11_P I/O LA12_N I/O GND DG GND DG 16

17 LA11_N I/O GND DG LA13_P I/O GND DG 17

18 GND DG LA16_P I/O LA13_N I/O LA14_P I/O 18

19 LA15_P I/O LA16_N I/O GND DG LA14_N I/O 19

20 LA15_N I/O GND DG LA17_P_CC I/O GND DG 20

21 GND DG LA20_P I/O LA17_N_CC I/O GND DG 21

22 LA19_P I/O LA20_N I/O GND DG LA18_P_CC I/O 22

23 LA19_N I/O GND DG LA23_P I/O LA18_N_CC I/O 23

24 GND DG LA22_P I/O LA23_N I/O GND DG 24

25 LA21_P I/O LA22_N I/O GND DG GND DG 25

26 LA21_N I/O GND DG LA26_P I/O LA27_P I/O 26

27 GND DG LA25_P I/O LA26_N I/O LA27_N I/O 27

28 LA24_P I/O LA25_N I/O GND DG GND DG 28

29 LA24_N I/O GND DG TCK 未使用 GND DG 29

30 GND DG LA29_P I/O TDI 未使用 SCL EEPROM 30

31 LA28_P I/O LA29_N I/O TDO 未使用 SDA EEPROM 31

32 LA28_N I/O GND DG 3P3VAUX EEPROM POW GND DG 32

33 GND DG LA31_P I/O TMS 未使用 GND DG 33

34 LA30_P I/O LA31_N I/O TRST_L 未使用 GA0 “0”固定 34

35 LA30_N I/O GND DG GA1 “0”固定 12P0V 12V 入力 35

36 GND DG LA33_P I/O 3P3V 3.3V入力 GND DG 36

37 LA32_P I/O LA33_N I/O GND DG 12P0V 12V 入力 37

38 LA32_N I/O GND DG 3P3V 3.3V入力 GND DG 38

39 GND DG VADJ VADJ GND DG 3P3V 3.3V入力 39

40 VADJ VADJ GND DG 3P3V 3.3V入力 GND DG 40

H G D C

Copyright©2015 Gigafirm Co.,Ltd. All Rights Reserved 27

GF43 ACA DE MINO 扱 明書

3.4.2 FMC コネ タと FPGA 間の接続 ン番号

Table 3-7 PCI Express ッ コ FPGA 間 接続 ン 示し

Table 3-7 FMC コ FPGA 間 接続 ン番号

コネ タ

ン番号

コネ タ

信号名

FPGA

ン番号

FPGA

信号名

I/O

信号 ベ

BANK

番号 D4 GBTCLK0_M2C_P F6 FMC1_GBTCLK0_M2C_P INPUT - 216 D5 GBTCLK0_M2C_N E6 FMC1_GBTCLK0_M2C_N INPUT - 216

C2 DP0_C2M_P B4 FMC1_GTP_TX0_P OUTPUT - 216

C3 DP0_C2M_N A4 FMC1_GTP_TX0_N OUTPUT - 216

C6 DP0_M2C_P B8 FMC1_GTP_RX0_P INPUT - 216

C7 DP0_M2C_N A8 FMC1_GTP_RX0_N INPUT - 216

H4 CLK0_M2C_P K18 FMC1_CLK0_M2C_P INPUT VADJ 15 H5 CLK0_M2C_N K19 FMC1_CLK0_M2C_N INPUT VADJ 15 G2 CLK1_M2C_P D17 FMC1_CLK1_M2C_P INPUT VADJ 16 G3 CLK1_M2C_N C17 FMC1_CLK1_M2C_N INPUT VADJ 16

G6 LA00_P_CC C18 FMC1_LA_P[0] BIDIR VADJ 16

G7 LA00_N_CC C19 FMC1_LA_N[0] BIDIR VADJ 16

D8 LA01_P_CC J19 FMC1_LA_P[1] BIDIR VADJ 15

D9 LA01_N_CC H19 FMC1_LA_N[1] BIDIR VADJ 15

H7 LA02_P F13 FMC1_LA_P[2] BIDIR VADJ 16

H8 LA02_N F14 FMC1_LA_N[2] BIDIR VADJ 16

G9 LA03_P B20 FMC1_LA_P[3] BIDIR VADJ 16

G10 LA03_N A20 FMC1_LA_N[3] BIDIR VADJ 16

H10 LA04_P F16 FMC1_LA_P[4] BIDIR VADJ 16

H11 LA04_N E17 FMC1_LA_N[4] BIDIR VADJ 16

D11 LA05_P J22 FMC1_LA_P[5] BIDIR VADJ 15

D12 LA05_N H22 FMC1_LA_N[5] BIDIR VADJ 15

C10 LA06_P H13 FMC1_LA_P[6] BIDIR VADJ 15

C11 LA06_N G13 FMC1_LA_N[6] BIDIR VADJ 15

H13 LA07_P C14 FMC1_LA_P[7] BIDIR VADJ 16

H14 LA07_N C15 FMC1_LA_N[7] BIDIR VADJ 16

G12 LA08_P A18 FMC1_LA_P[8] BIDIR VADJ 16

Copyright©2015 Gigafirm Co.,Ltd. All Rights Reserved 28

GF43 ACA DE MINO 扱 明書

コネ タ

ン番号

コネ タ

信号名

FPGA

ン番号

FPGA

信号名

I/O

信号 ベ

BANK

番号

G13 LA08_N A19 FMC1_LA_N[8] BIDIR VADJ 16

D14 LA09_P H20 FMC1_LA_P[9] BIDIR VADJ 15

D15 LA09_N G20 FMC1_LA_N[9] BIDIR VADJ 15

C14 LA10_P G15 FMC1_LA_P[10] BIDIR VADJ 15

C15 LA10_N G16 FMC1_LA_N[10] BIDIR VADJ 15

H16 LA11_P E13 FMC1_LA_P[11] BIDIR VADJ 16

H17 LA11_N E14 FMC1_LA_N[11] BIDIR VADJ 16

G15 LA12_P F19 FMC1_LA_P[12] BIDIR VADJ 16

G16 LA12_N F20 FMC1_LA_N[12] BIDIR VADJ 16

D17 LA13_P K21 FMC1_LA_P[13] BIDIR VADJ 15

D18 LA13_N K22 FMC1_LA_N[13] BIDIR VADJ 15

C18 LA14_P J14 FMC1_LA_P[14] BIDIR VADJ 15

C19 LA14_N H14 FMC1_LA_N[14] BIDIR VADJ 15

H19 LA15_P E16 FMC1_LA_P[15] BIDIR VADJ 16

H20 LA15_N D16 FMC1_LA_N[15] BIDIR VADJ 16

G18 LA16_P C22 FMC1_LA_P[16] BIDIR VADJ 16

G19 LA16_N B22 FMC1_LA_N[16] BIDIR VADJ 16

D20 LA17_P_CC J20 FMC1_LA_P[17] BIDIR VADJ 15 D21 LA17_N_CC J21 FMC1_LA_N[17] BIDIR VADJ 15 C22 LA18_P_CC L19 FMC1_LA_P[18] BIDIR VADJ 15 C23 LA18_N_CC L20 FMC1_LA_N[18] BIDIR VADJ 15

H22 LA19_P B15 FMC1_LA_P[19] BIDIR VADJ 16

H23 LA19_N B16 FMC1_LA_N[19] BIDIR VADJ 16

G21 LA20_P B21 FMC1_LA_P[20] BIDIR VADJ 16

G22 LA20_N A21 FMC1_LA_N[20] BIDIR VADJ 16

H25 LA21_P C13 FMC1_LA_P[21] BIDIR VADJ 16

H26 LA21_N B13 FMC1_LA_N[21] BIDIR VADJ 16

Copyright©2015 Gigafirm Co.,Ltd. All Rights Reserved 29

GF43 ACA DE MINO 扱 明書

コネ タ

ン番号

コネ タ

信号名

FPGA

ン番号

FPGA

信号名

I/O

信号 ベ

BANK

番号

G24 LA22_P E22 FMC1_LA_P[22] BIDIR VADJ 16

G25 LA22_N D22 FMC1_LA_N[22] BIDIR VADJ 16

D23 LA23_P M18 FMC1_LA_P[23] BIDIR VADJ 15

D24 LA23_N L18 FMC1_LA_N[23] BIDIR VADJ 15

H28 LA24_P A15 FMC1_LA_P[24] BIDIR VADJ 16

H29 LA24_N A16 FMC1_LA_N[24] BIDIR VADJ 16

G27 LA25_P E21 FMC1_LA_P[25] BIDIR VADJ 16

G28 LA25_N D21 FMC1_LA_N[25] BIDIR VADJ 16

D26 LA26_P N18 FMC1_LA_P[26] BIDIR VADJ 15

D27 LA26_N N19 FMC1_LA_N[26] BIDIR VADJ 15

C26 LA27_P J15 FMC1_LA_P[27] BIDIR VADJ 15

C27 LA27_N H15 FMC1_LA_N[27] BIDIR VADJ 15

H31 LA28_P A13 FMC1_LA_P[28] BIDIR VADJ 16

H32 LA28_N A14 FMC1_LA_N[28] BIDIR VADJ 16

G30 LA29_P G21 FMC1_LA_P[29] BIDIR VADJ 16

G31 LA29_N G22 FMC1_LA_N[29] BIDIR VADJ 16

H34 LA30_P M21 FMC1_LA_P[30] BIDIR VADJ 15

H35 LA30_N L21 FMC1_LA_N[30] BIDIR VADJ 15

G33 LA31_P M13 FMC1_LA_P[31] BIDIR VADJ 15

G34 LA31_N L13 FMC1_LA_N[31] BIDIR VADJ 15

H37 LA32_P F18 FMC1_LA_P[32] BIDIR VADJ 16

H38 LA32_N E18 FMC1_LA_N[32] BIDIR VADJ 16

G36 LA33_P K17 FMC1_LA_P[33] BIDIR VADJ 15

G37 LA33_N J17 FMC1_LA_N[33] BIDIR VADJ 15

D1 PG_C2M Y22 ARD_RESET INPUT LVCMOS33 14

H2 PRSNT_M2C_L W22 FMC1_PRSNT_M2C_L INPUT LVCMOS33 14

C30 SCL AA20 FMC1_SCL BIDIR LVCMOS33 14

C31 SDA AA21 FMC1_SDA BIDIR LVCMOS33 14

Copyright©2015 Gigafirm Co.,Ltd. All Rights Reserved 30

GF43 ACA DE MINO 扱 明書

3.5 Arduino コネ タ CN6-CN9

本 Arduino コ Arduino 対応し 接続し 使用

3.5.1 Arduino コネ タ ン配置

Table 3-8 ~ 3-11 Arduino コ ン配置 示し

Table 3-8 CN6 ン配置

ン番号 名称 機能

1 NC 未接続

2 IOREF IO用電源 ARD_BUFVCCに接続

3 RESET セッ

4 3.3V 3.3V電源

5 5V 5V電源

6 GND 電源GND

7 GND 電源GND

8 VIN 12V電源

Table 3-9 CN7 ン配置

ン番号 名称 機能

1 D0(RX) タ IO

2 D1(TX) タ IO

3 D2 タ IO

4 D3 タ IO

5 D4 タ IO

6 D5 タ IO

7 D6 タ IO

8 D7 タ IO

Copyright©2015 Gigafirm Co.,Ltd. All Rights Reserved 31

GF43 ACA DE MINO 扱 明書

Table 3-10 CN8 ン配置

ン番号 名称 機能

1 D8 タ IO

2 D9 タ IO

3 D10 タ IO

4 D11 タ IO

5 D12 タ IO

6 D13 タ IO

7 GND 電源GND

8 ARD_AREF ン 未接続

9 D14(SDA) タ IO 10 D15(SCL) タ IO

Table 3-11 CN9 ン配置

ン番号 名称 機能

1 A0 / タ 兼用 IO

2 A1 / タ 兼用 IO

3 A2 / タ 兼用 IO

4 A3 / タ 兼用 IO

5 A4 / タ 兼用 IO

6 A5 / タ 兼用 IO

Copyright©2015 Gigafirm Co.,Ltd. All Rights Reserved 32

GF43 ACA DE MINO 扱 明書

3.5.2 Arduino コネ タと FPGA 間の接続 ン番号

Table 3-12 ~ 14 Arduino コ FPGA 間 接続 ン 示し

Table 3-12 CN6,CN7 FPGA 間 接続 ン

コネ タ

ン番号

コネ タ

信号名

FPGA

ン番号

FPGA

信号名

I/O

信号 ベ

BANK

番号 CN6 3 RESET

Y22 ARD_RESET BIDIR LVCMOS33 14 AB21 ARD_RESET_CNT OUTPUT LVCMOS33 14

CN7

1 D0(RX)

R6 FPGA_ARD[0] BIDIR ARD_BUFVCCA 34 T6 FPGA_ARD_CNT[0] OUTPUT ARD_BUFVCCA 34

2 D1(TX)

H4 FPGA_ARD[1] BIDIR ARD_BUFVCCA 35 G4 FPGA_ARD_CNT[1] OUTPUT ARD_BUFVCCA 35

3 D2

U5 FPGA_ARD[2] BIDIR ARD_BUFVCCA 34 V5 FPGA_ARD_CNT[2] OUTPUT ARD_BUFVCCA 34

4 D3

Y6 FPGA_ARD[3] BIDIR ARD_BUFVCCA 34 T3 FPGA_ARD_CNT[3] OUTPUT ARD_BUFVCCA 34

5 D4

AA6 FPGA_ARD[4] BIDIR ARD_BUFVCCA 34 U7 FPGA_ARD_CNT[4] OUTPUT ARD_BUFVCCA 34

6 D5

J5 FPGA_ARD[5] BIDIR ARD_BUFVCCA 35 H5 FPGA_ARD_CNT[5] OUTPUT ARD_BUFVCCA 35

7 D6

H3 FPGA_ARD[6] BIDIR ARD_BUFVCCA 35 G3 FPGA_ARD_CNT[6] OUTPUT ARD_BUFVCCA 35

8 D7

F3 FPGA_ARD[7] BIDIR ARD_BUFVCCA 35 T1 FPGA_ARD_CNT[7] OUTPUT ARD_BUFVCCA 34

Copyright©2015 Gigafirm Co.,Ltd. All Rights Reserved 33

GF43 ACA DE MINO 扱 明書

Table 3-13 CN8 FPGA 間 接続 ン

コネ タ

ン番号

コネ タ

信号名

FPGA

ン番号

FPGA

信号名

I/O

信号 ベ

BANK

番号

CN8

1 D8

K4 FPGA_ARD[8] BIDIR ARD_BUFVCCA 35 J4 FPGA_ARD_CNT[8] OUTPUT ARD_BUFVCCA 35

2 D9

K3 FPGA_ARD[9] BIDIR ARD_BUFVCCA 35 L3 FPGA_ARD_CNT[9] OUTPUT ARD_BUFVCCA 35

3 D10

M1 FPGA_ARD[10] BIDIR ARD_BUFVCCA 35 L1 FPGA_ARD_CNT[10] OUTPUT ARD_BUFVCCA 35

4 D11

M3 FPGA_ARD[11] BIDIR ARD_BUFVCCA 35 M2 FPGA_ARD_CNT[11] OUTPUT ARD_BUFVCCA 35

5 D12

K6 FPGA_ARD[12] BIDIR ARD_BUFVCCA 35 J6 FPGA_ARD_CNT[12] OUTPUT ARD_BUFVCCA 35

6 D13

T20 FPGA_ARD[13] BIDIR LVCMOS33 14 W21 FPGA_ARD_CNT[13] OUTPUT LVCMOS33 14

9 D14(SDA)

G17 FPGA_ARD[14] BIDIR VADJ 15 G18 FPGA_ARD_CNT[14] OUTPUT VADJ 15

10 D15(SCL)

N22 FPGA_ARD[15] BIDIR VADJ 15 M22 FPGA_ARD_CNT[15] OUTPUT VADJ 15

Copyright©2015 Gigafirm Co.,Ltd. All Rights Reserved 34

GF43 ACA DE MINO 扱 明書

Table 3-14 CN9 FPGA 間 接続 ン

コネ タ

ン番号

コネ タ

信号名

FPGA

ン番号

FPGA

信号名

I/O

信号 ベ

BANK

番号

CN9

1 A0

B1 FPGA_ARA_P[0] INPUT ARD_BUFVCCA 35 A1 FPGA_ARA_N[0] INPUT GND 35 E2 FPGA_ARA_CNT[0] OUTPUT ARD_BUFVCCA 35

2 A1

E1 FPGA_ARA_P[1] INPUT ARD_BUFVCCA 35 D1 FPGA_ARA_N[1] INPUT GND 35 D2 FPGA_ARA_CNT[1] OUTPUT ARD_BUFVCCA 35

3 A2

K1 FPGA_ARA_P[2] INPUT ARD_BUFVCCA 35 J1 FPGA_ARA_N[2] INPUT GND 35 H2 FPGA_ARA_CNT[2] OUTPUT ARD_BUFVCCA 35

4 A3

K2 FPGA_ARA_P[3] INPUT ARD_BUFVCCA 35 J2 FPGA_ARA_N[3] INPUT GND 35 G2 FPGA_ARA_CNT[3] OUTPUT ARD_BUFVCCA 35

5 A4

C2 FPGA_ARA_P[4] INPUT ARD_BUFVCCA 35 B2 FPGA_ARA_N[4] INPUT GND 35 L5 FPGA_ARA_CNT[4] OUTPUT ARD_BUFVCCA 35

6 A5

G1 FPGA_ARA_P[5] INPUT ARD_BUFVCCA 35 F1 FPGA_ARA_N[5] INPUT GND 35 L4 FPGA_ARA_CNT[5] OUTPUT ARD_BUFVCCA 35

Copyright©2015 Gigafirm Co.,Ltd. All Rights Reserved 35

GF43 ACA DE MINO 扱 明書

3.5.3 Arduino コネ タバッ 制御 ジタ IO

Arduino +5V 動作 多い 本 FPGA Arduino コ 間

ベ 変換 ッ 挿入し い

従 Arduino FPGA 間 接続し 使用 本 ッ 有効 必要

あ

逆 FPGA Arduino 使用し い場合 本 ッ 無効 し 使用し

い

FPGA_ARD_CNT[n] = „1‟ : 有効 „0‟ 無効

FPGA_ARA_CNT[n] = „1‟ : 有効 „0‟ 無効

TXB0101 A EN

B R

CN7

TXB0101 A EN

B R

CN8

TXB0101 A EN

B R

CN9 R'

FPGA FPGA_ARD[0] FPGA_ARD_CNT[0]

FPGA_ARD[15] FPGA_ARD_CNT[15]

FPGA_ARA[0] FPGA_ARA_CNT[0]

ARD_D0

ARD_D15

ARD_A0

Figure 3-4 Arduino コ ッ

Copyright©2015 Gigafirm Co.,Ltd. All Rights Reserved 36

GF43 ACA DE MINO 扱 明書

3.5.4 Arduino ロ 入力

本 FPGA 内蔵 XADC 使用し Arduino コ 入力 使用

可能

本機能 使用 場合 Figure 3-4 ARD_A0 ~ A5 信号 R 抵抗 外し R ‟ 位置

移動 必要 あ

Table 3-15 本抵抗位置一覧 示し

Table 3-15 Arduino 入力設定抵抗一覧

ン番号 名称 R R'

1 A0 R71 R77

2 A1 R72 R78

3 A2 R73 R79

4 A3 R74 R80

5 A4 R75 R81

6 A5 R76 R82

FPGA 内蔵 XADC 制限 本 最大入力 ベ 以 値

入力 本 ベ 以 い う 使用 願い致し

AP203 : +1.5V以 AS501 : +1.5V以

Copyright©2015 Gigafirm Co.,Ltd. All Rights Reserved 37

GF43 ACA DE MINO 扱 明書

3.6 FPGA 拡張 IO ポー CN 11

本 FPGA 直接接続 い 20 本 汎用入出力信号 使用

Table 3-16 CN11 推奨コ 様

コネ タ

番号

ン 数

コネ タ型格 ーカ 備考

CN12 12 SSW-106-02-G-D-RA Samtec Inc. 個使用

3.6.1 FPGA 拡張 IO ポー ン配置

Table 3-17 FPGA 拡張 IO コ ン配置 示し

本 ン配置 い ン番号 1 ~ 12 ン番号 19 ~ 20 PMOD モ

一配置 い PMOD モ 使用 可能

し PMOD ン番号 振 方 異 注意し い

Table 3-18,Table3-19 PMOD モ ン番号対応表 示し

Table 3-17 FPGA 拡張 IO コ ン配置

ン番号 名称 機能 ン番号 名称 機能

1 PORT1_00 タ IO 2 PORT1_02 タ IO

3 PORT1_01 タ IO 4 PORT1_03 タ IO

5 PORT1_04 タ IO 6 PORT1_06 タ IO

7 PORT1_05 タ IO 8 PORT1_07 タ IO

9 GND 電源GND 10 GND 電源GND

11 3.3V 3.3V電源 12 3.3V 3.3V電源

13 PORT1_08 タ IO 14 PORT1_10 タ IO

15 PORT1_09 タ IO 16 PORT1_11 タ IO

17 GND 電源GND 18 5V 5V電源

19 PORT1_12 タ IO 20 PORT1_14 タ IO

21 PORT1_13 タ IO 22 PORT1_15 タ IO

23 PORT1_16 タ IO 24 PORT1_18 タ IO

25 PORT1_17 タ IO 26 PORT1_19 タ IO

27 GND 電源GND 28 GND 電源GND

29 3.3V 3.3V電源 30 3.3V 3.3V電源

Copyright©2015 Gigafirm Co.,Ltd. All Rights Reserved 38

GF43 ACA DE MINO 扱 明書

Table 3-18 PMOD コ ン番号対応表

EXTEND CN PMOD CN

ン番 号

名称 機能

ン番 号

機能

1 PORT1_00 タ IO 2 タ IO

2 PORT1_02 タ IO 1 タ IO

3 PORT1_01 タ IO 4 タ IO

4 PORT1_03 タ IO 3 タ IO

5 PORT1_04 タ IO 6 タ IO

6 PORT1_06 タ IO 5 タ IO

7 PORT1_05 タ IO 8 タ IO

8 PORT1_07 タ IO 7 タ IO

9 GND 電源GND 10 電源GND

10 GND 電源GND 9 電源GND

11 3.3V 3.3V電源 12 3.3V電源

12 3.3V 3.3V電源 11 3.3V電源

Table 3-19 PMOD コ ン番号対応表

EXTEND CN PMOD CN

ン番 号

名称 機能

ン番 号

機能

19 PORT1_12 タ IO 2 タ IO

20 PORT1_14 タ IO 1 タ IO

21 PORT1_13 タ IO 4 タ IO

22 PORT1_15 タ IO 3 タ IO

23 PORT1_16 タ IO 6 タ IO

24 PORT1_18 タ IO 5 タ IO

25 PORT1_17 タ IO 8 タ IO

26 PORT1_19 タ IO 7 タ IO

27 GND 電源GND 10 電源GND

28 GND 電源GND 9 電源GND

29 3.3V 3.3V電源 12 3.3V電源

30 3.3V 3.3V電源 11 3.3V電源

Copyright©2015 Gigafirm Co.,Ltd. All Rights Reserved 39

GF43 ACA DE MINO 扱 明書

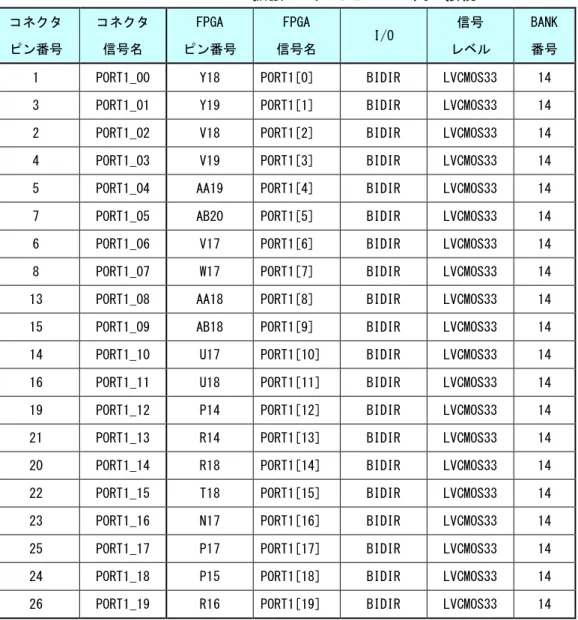

3.6.2 FPGA 拡張 IO ポー と FPGA 間の接続 ン番号

Table 3-20 FPGA 拡張 IO FPGA 間 接続 ン 示し

Table 3-20 FPGA 拡張 IO FPGA 間 接続 ン

コネ タ

ン番号

コネ タ

信号名

FPGA

ン番号

FPGA

信号名

I/O

信号 ベ

BANK

番号 1 PORT1_00 Y18 PORT1[0] BIDIR LVCMOS33 14 3 PORT1_01 Y19 PORT1[1] BIDIR LVCMOS33 14 2 PORT1_02 V18 PORT1[2] BIDIR LVCMOS33 14 4 PORT1_03 V19 PORT1[3] BIDIR LVCMOS33 14 5 PORT1_04 AA19 PORT1[4] BIDIR LVCMOS33 14 7 PORT1_05 AB20 PORT1[5] BIDIR LVCMOS33 14 6 PORT1_06 V17 PORT1[6] BIDIR LVCMOS33 14 8 PORT1_07 W17 PORT1[7] BIDIR LVCMOS33 14 13 PORT1_08 AA18 PORT1[8] BIDIR LVCMOS33 14 15 PORT1_09 AB18 PORT1[9] BIDIR LVCMOS33 14 14 PORT1_10 U17 PORT1[10] BIDIR LVCMOS33 14 16 PORT1_11 U18 PORT1[11] BIDIR LVCMOS33 14 19 PORT1_12 P14 PORT1[12] BIDIR LVCMOS33 14 21 PORT1_13 R14 PORT1[13] BIDIR LVCMOS33 14 20 PORT1_14 R18 PORT1[14] BIDIR LVCMOS33 14 22 PORT1_15 T18 PORT1[15] BIDIR LVCMOS33 14 23 PORT1_16 N17 PORT1[16] BIDIR LVCMOS33 14 25 PORT1_17 P17 PORT1[17] BIDIR LVCMOS33 14 24 PORT1_18 P15 PORT1[18] BIDIR LVCMOS33 14 26 PORT1_19 R16 PORT1[19] BIDIR LVCMOS33 14

Copyright©2015 Gigafirm Co.,Ltd. All Rights Reserved 40

GF43 ACA DE MINO 扱 明書

3.7 DDR3

本 2G bit DDR3 SDRAM 搭載し い

Xilinx MIG IP ン配置 合わ い 本 IP 使用 DDR3 SDRAM

利用可能

3.7.1 DDR3 SDRAM と FPGA 間の接続 ン番号

Table 3-21 DDR3 SDRAM FPGA 間 接続 ン 示し

Table 3-21 DDR3 SDRAM FPGA 間 接続 ン

DDR3ン番号

DDR3

信号名

FPGA

ン番号

FPGA

信号名

I/O

信号 ベ

BANK

番号

N3 A0 AA3 ddr3_addr[0] OUTPUT SSTL15 34

P7 A1 Y3 ddr3_addr[1] OUTPUT SSTL15 34

P3 A2 W2 ddr3_addr[2] OUTPUT SSTL15 34

N2 A3 V2 ddr3_addr[3] OUTPUT SSTL15 34

P8 A4 U2 ddr3_addr[4] OUTPUT SSTL15 34

P2 A5 U1 ddr3_addr[5] OUTPUT SSTL15 34

R8 A6 AB2 ddr3_addr[6] OUTPUT SSTL15 34

R2 A7 AB3 ddr3_addr[7] OUTPUT SSTL15 34

T8 A8 AB1 ddr3_addr[8] OUTPUT SSTL15 34

R3 A9 AA1 ddr3_addr[9] OUTPUT SSTL15 34

L7 A10 U3 ddr3_addr[10] OUTPUT SSTL15 34

R7 A11 Y1 ddr3_addr[11] OUTPUT SSTL15 34

N7 A12 W1 ddr3_addr[12] OUTPUT SSTL15 34

T3 A13 Y2 ddr3_addr[13] OUTPUT SSTL15 34

M2 BA0 Y4 ddr3_ba[0] OUTPUT SSTL15 34

N8 BA1 AB5 ddr3_ba[1] OUTPUT SSTL15 34

M3 BA2 AA5 ddr3_ba[2] OUTPUT SSTL15 34

K3 CAS_N V4 ddr3_cas_n OUTPUT SSTL15 34

K9 CKE R3 ddr3_ck_n[0] OUTPUT SSTL15 34

J7 CK_P W5 ddr3_ck_p[0] OUTPUT DIFF_SSTL15 34

K7 CK_N R2 ddr3_cke[0] OUTPUT DIFF_SSTL15 34

L2 CS_N W6 ddr3_cs_n[0] OUTPUT SSTL15 34

Copyright©2015 Gigafirm Co.,Ltd. All Rights Reserved 41

GF43 ACA DE MINO 扱 明書

DDR3

ン番号

DDR3

信号名

FPGA

ン番号

FPGA

信号名

I/O

信号 ベ

BANK

番号

E7 DM0 N4 ddr3_dm[0] OUTPUT SSTL15 35

D3 DM1 V7 ddr3_dm[1] OUTPUT SSTL15 34

K1 ODT U6 ddr3_odt[0] OUTPUT SSTL15 34

J3 RAS_N AA4 ddr3_ras_n OUTPUT SSTL15 34

T2 RESET_N T5 ddr3_reset_n OUTPUT LVCMOS15 34

L3 WE_N W4 ddr3_we_n OUTPUT SSTL15 34

E3 DQ0 R1 ddr3_dq[0] BIDIR SSTL15 35

F7 DQ1 P1 ddr3_dq[1] BIDIR SSTL15 35

F2 DQ2 P2 ddr3_dq[2] BIDIR SSTL15 35

F8 DQ3 N2 ddr3_dq[3] BIDIR SSTL15 35

H3 DQ4 M6 ddr3_dq[4] BIDIR SSTL15 35

H8 DQ5 M5 ddr3_dq[5] BIDIR SSTL15 35

G2 DQ6 P6 ddr3_dq[6] BIDIR SSTL15 35

H7 DQ7 N5 ddr3_dq[7] BIDIR SSTL15 35

D7 DQ8 AB7 ddr3_dq[8] BIDIR SSTL15 34

C3 DQ9 AB6 ddr3_dq[9] BIDIR SSTL15 34

C8 DQ10 AA8 ddr3_dq[10] BIDIR SSTL15 34

C2 DQ11 AB8 ddr3_dq[11] BIDIR SSTL15 34

A7 DQ12 Y8 ddr3_dq[12] BIDIR SSTL15 34

A2 DQ13 Y7 ddr3_dq[13] BIDIR SSTL15 34

B8 DQ14 W9 ddr3_dq[14] BIDIR SSTL15 34

A3 DQ15 Y9 ddr3_dq[15] BIDIR SSTL15 34

F3 DQSP0 P5 ddr3_dqs_p[0] BIDIR DIFF_SSTL15 35 G3 DQSN0 P4 ddr3_dqs_n[0] BIDIR DIFF_SSTL15 35 C7 DQSP1 V9 ddr3_dqs_p[1] BIDIR DIFF_SSTL15 34 B7 DQSN1 V8 ddr3_dqs_n[1] BIDIR DIFF_SSTL15 34

Copyright©2015 Gigafirm Co.,Ltd. All Rights Reserved 42

GF43 ACA DE MINO 扱 明書

3.8 HDMI コネ タ CN12

本 HDMI コ 搭載し い FPGA HDMI 出力回路 実装

HDMI 出力 利用 可能

3.8.1 HDMI コネ タ ン配置

Table 3-22 HDMI コ ン配置 示し

Table 3-22 HDMI コ ン配置

ン番号 名称 機能

1 D2+ TMDS Data 2+

2 D2S TMDS Data 2 ー

3 D2- TMDS Data 2- 4 D1+ TMDS Data 1+

5 D1S TMDS Data 1 ー

6 D1- TMDS Data 1- 7 D0+ TMDS Data 0+

8 D0S TMDS Data 0 ー

9 D0- TMDS Data 0-

10 CLK+ TMDS Data ッ +

11 CLKS TMDS Data ッ ー

12 CLK- TMDS Data ッ -

13 CEC CEC イン

14 RES 予備

15 SCL DDC ッ DDC/SCL

16 SDA DDC ータ DDC/SDA

17 DDC/CECG GND for +5V

18 5VP +5V

19 HPD HOT Plug Detec

Copyright©2015 Gigafirm Co.,Ltd. All Rights Reserved 43

GF43 ACA DE MINO 扱 明書

3.8.2 HDMI コネ タと FPGA 間の接続 ン番号

Table 3-23 HDMI コ FPGA 間 接続 ン 示し

Table 3-23 HDMI コ FPGA 間 接続 ン番号

コネ タ

ン番号

コネ タ

信号名

FPGA

ン番号

FPGA

信号名

I/O

信号 ベ

BANK

番号

1 D2+ AB11 HDMI_D2_P OUTPUT TMDS_33 13

3 D2- AB12 HDMI_D2_N OUTPUT TMDS_33 13

4 D1+ Y13 HDMI_D1_P OUTPUT TMDS_33 13

6 D1- AA14 HDMI_D1_N OUTPUT TMDS_33 13

7 D0+ AA15 HDMI_D0_P OUTPUT TMDS_33 13

9 D0- AB15 HDMI_D0_N OUTPUT TMDS_33 13

10 CLK+ W11 HDMI_CLK_P OUTPUT TMDS_33 13

13 CEC W12 HDMI_CLK_N OUTPUT TMDS_33 13

15 SCL AA16 HDMI_CEC BIDIR LVCMOS33 13

16 SDA AB16 HDMI_SCL BIDIR LVCMOS33 13

17 DDC/CECG AB17 HDMI_SDA BIDIR LVCMOS33 13

19 HPD Y16 HDMI_HPD BIDIR LVCMOS33 13

Copyright©2015 Gigafirm Co.,Ltd. All Rights Reserved 44

GF43 ACA DE MINO 扱 明書

3.9 U.FL コネ タ CN13 ~ CN16

本 FPGA 直接接続 4 本 U.FL 入出力信号 搭載し い

本信号 ン ン 差動信号 し 使用可能

3.9.1 U.FL コネ タと FPGA 間の接続 ン番号

Table 3-24 U.FL コ FPGA 間 接続 ン 示し

Table 3-24 U.FL コ FPGA 間 接続 ン番号

コネ タ

番号

コネ タ

信号名

FPGA

ン番号

FPGA

信号名

I/O

信号 ベ

BANK

番号

CN13 IO0+ B17 FPGA_DIFF_IO0_P BIDIR VADJ 16

CN14 IO0- B18 FPGA_DIFF_IO0_N BIDIR VADJ 16

CN15 IO1+ E19 FPGA_DIFF_IO1_P BIDIR VADJ 16

CN16 IO1- D19 FPGA_DIFF_IO1_N BIDIR VADJ 16

Copyright©2015 Gigafirm Co.,Ltd. All Rights Reserved 45

GF43 ACA DE MINO 扱 明書

3.10 SATA コネ タ

本 SATA コ 搭載 SATA コ 実装し FPGA

SATA 制御回路 搭載 SATA ン 利用

3.10.1 SATA コネ タ ン配置

Table 3-25 SATA コ ン配置 示し

Table 3-25 SATA コ ン配置

ン番号 名称 機能

1 GND GND

2 HTX+ 送信 ータ+

3 HTX- 送信 ータ-

4 GND GND

5 HRX- 受信 ータ+

6 HRX+ 受信 ータ-

7 GND GND

3.10.2 FPGA との接続 ン番号

Table 3-26 SATA コ FPGA 間 接続 ン 示し

Table 3-26 SATA コ FPGA 間 接続 ン

コネ タ

ン番号

コネ タ

信号名

FPGA

ン番号

FPGA

信号名

I/O

信号 ベ

BANK

番号

2 HTX+ D5 GTP_TXP2 OUTPUT - 216

3 HTX- C5 GTP_TXN2 OUTPUT - 216

5 HRX- D11 GTP_RXP2 INPUT - 216

6 HRX+ C11 GTP_RXN2 INPUT - 216

Copyright©2015 Gigafirm Co.,Ltd. All Rights Reserved 46

GF43 ACA DE MINO 扱 明書

3.11 7 seg.LED

本 7seg.LED 搭載し FPGA 制御 7seg.LED 表示

可能

7seg.LED FPGA 間 接続 ソ 側 共通 い 交互 ッ

点灯 う 制御し い

DSP_LED_A DSP_LED_B DSP_LED_C DSP_LED_D DSP_LED_E DSP_LED_F DSP_LED_G DSP_LED_DP DSP_LEDCOM1 DSP_LEDCOM0

+3.3V

a b c d e f g dp

LED2 LED1

COM

COM FPGA

Figure 3-5 7seg.LED 接続図

Copyright©2015 Gigafirm Co.,Ltd. All Rights Reserved 47

GF43 ACA DE MINO 扱 明書

3.11.1 7seg.LED と FPGA 間の接続 ン番号

Table 3-27 7seg.LED FPGA 間 接続 ン 示し

Table 3-27 7seg.LED FPGA 間 接続 ン番号

7segン番号

7seg

信号名

FPGA

ン番号

FPGA

信号名

I/O

信号 ベ

BANK

番号

制御

3,8 COMMON P20 DSP_LEDCOM0 OUTPUT LVCMOS33 14 L' ON 3,8 COMMON AB22 DSP_LEDCOM1 OUTPUT LVCMOS33 14 L' ON 7 Cathode A N20 DSP_LED_A OUTPUT LVCMOS33 15 H' ON 6 Cathode B M20 DSP_LED_B OUTPUT LVCMOS33 15 H' ON 4 Cathode C L14 DSP_LED_C OUTPUT LVCMOS33 15 H' ON 2 Cathode D L15 DSP_LED_D OUTPUT LVCMOS33 15 H' ON 1 Cathode E L16 DSP_LED_E OUTPUT LVCMOS33 15 H' ON 9 Cathode F K16 DSP_LED_F OUTPUT LVCMOS33 15 H' ON 10 Cathode G M15 DSP_LED_G OUTPUT LVCMOS33 15 H' ON 5 Cathode DP M16 DSP_LED_DP OUTPUT LVCMOS33 15 H' ON

Copyright©2015 Gigafirm Co.,Ltd. All Rights Reserved 48

GF43 ACA DE MINO 扱 明書

3.12 STATUS LED

本 FPGA 制御可能 LED 個搭載し い

3.12.1 STATUS LED と FPGA 間の接続 ン番号

Table 3-28 STATUS LED FPGA 間 接続 ン 示し

Table 3-28 STATUS LED FPGA 間 接続 ン番号

LED番号

LED名 FPGA

ン番号

FPGA

信号名

I/O

信号 ベ

BANK

番号

制御

LED4 STATUS0 T21 DBG_LED[0] OUTPUT LVCMOS33 14 L' ON LED5 STATUS1 U21 DBG_LED[1] OUTPUT LVCMOS33 14 L' ON LED6 STATUS2 P19 DBG_LED[2] OUTPUT LVCMOS33 14 L' ON LED7 STATUS3 R19 DBG_LED[3] OUTPUT LVCMOS33 14 L' ON

3.13 DIPSW

本 FPGA 可能 DIPSW(4bit) 個搭載し い

3.13.1 DIPSW と FPGA 間の接続 ン番号

Table 3-29 DIPSW FPGA 間 接続 ン 示し

Table 3-29 DIPSW FPGA 間 接続 ン

DIPSW番号

DIPSW 信号名

FPGA ン番号

FPGA

信号名 I/O

信号

ベ

BANK 番号

備考

1 DSW1 N13 DBG_DSW[0] INPUT LVCMOS33 14 L' ON

2 DSW2 N14 DBG_DSW[1] INPUT LVCMOS33 14 L' ON

3 DSW3 P16 DBG_DSW[2] INPUT LVCMOS33 14 L' ON

4 DSW4 R17 DBG_DSW[3] INPUT LVCMOS33 14 L' ON

Copyright©2015 Gigafirm Co.,Ltd. All Rights Reserved 49

GF43 ACA DE MINO 扱 明書

3.14 PUSH SW

本 2 個 専用 PUSH SW FPGA 可能 個 Pusw SW

搭載し い

3.14.1 専用 PUSH SW

専用 PUSH SW FPGA コン ン用 全体 セッ 用

搭載し い

Table 3-30 専用 PUSH SW

PUSH SW番号

PUSH SW

名

用途 備考

SW2 CONFIG FPGA Configuration 開始 L' ON

SW3 RESET ー セッ L' ON

3.14.2 ユーザー用 PUSW SW と FPGA 間の接続 ン番号

Table 3-31 用 PUSW SW FPGA 間 接続 ン 示し

Table 3-31 用 PUSW SW FPGA 間 接続 ン番号

PUSH SW

番号

PUSH SW

名

FPGA

ン番号

FPGA

信号名

I/O

信号 ベ

BANK

番号

備考 SW4 TST1 F4 DBG_PSW[0] INPUT ARD_BUFVCCA 35 L' ON SW5 TST2 L6 DBG_PSW[1] INPUT ARD_BUFVCCA 35 L' ON